# Part I: Mixed-Signal Performance of Various High-Voltage Drain-Extended MOS Devices

Mayank Shrivastava, *Student Member, IEEE*, Maryam Shojaei Baghini, *Senior Member, IEEE*, Harald Gossner, *Member, IEEE*, and V. Ramgopal Rao, *Senior Member, IEEE*

Abstract—In this paper, the optimization issues of various drain-extended devices are discussed for input/output applications. The mixed-signal performance, impact of process variations, and gate oxide reliability of these devices are compared. Lightly doped drain MOS (LDDMOS) was found to have a moderate performance advantage as compared to shallow trench isolation (STI) and non-STI drain-extended MOS (DeMOS) devices. Non-STI DeMOS devices have improved circuit performance but suffer from the worst gate oxide reliability. Incorporating an STI region underneath the gate—drain overlap improves the gate oxide reliability, although it degrades the mixed-signal characteristics of the device. The single-halo nature of DeMOS devices has been shown to be effective in suppressing the short-channel effects.

*Index Terms*—Drain-extended MOS (DeMOS), hot carrier, input/output, lightly doped drain MOS (LDDMOS), mixed signal, reduced surface field (RESURF), reliability.

### I. INTRODUCTION

TOWADAYS, electronic systems often have multiple semiconductor chips fabricated in different CMOS technologies handling different functionalities like voltage regulation, signal conditioning, data conversion, and digital processing. Many integrated circuits like system-on-chips (SOCs) consist of multiple embedded CMOS technologies. On the other hand, with the continued scaling of devices in advanced digital CMOS technologies, the power supply voltage is also getting scaled to reduce the power consumption and to meet the gate oxide reliability. Therefore, interfacing the semiconductor chips or subsystems on the chip, having different levels of supply voltage, and satisfying the speed and noise requirements are becoming crucial from the overall performance point of view. For example, a digital processing chip working with a supply voltage of 2 V may interact with a peripheral chip with a supply voltage of 12 V. The I/O circuit design should be allowed to span the entire design space that the logic design enjoys. However, constraints like undesired leakage current paths between chips [1], [2], electrical overstress across the gate oxide [3],

Manuscript received April 17, 2009; revised November 2, 2009 First published December 8, 2009; current version published January 22, 2010. The work of M. Shrivastava was supported by an Infineon Fellowship at Indian Institute of Technology Bombay, Mumbai, India. The review of this paper was arranged by Editor H. S. Momose.

M. Shrivastava, M. Shojaei Baghini, and V. R. Rao are with the Center for Nanoelectronics, Department of Electrical Engineering, Indian Institute of Technology Bombay, Mumbai 400076, India (e-mail: mayank@ee.iitb.ac.in; rrao@ee.iitb.ac.in).

H. Gossner is with Infineon Technology AG, 81609 Munich, Germany (e-mail: Harald.Gossner@infineon.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2036796

and hot carrier degradation [4] in I/O design take away the flexibility.

One of the bottlenecks for introducing CMOS I/O circuits is their susceptibility to electrostatic discharge (ESD). It is due to both the gate oxide breakdown and junction-degradation-related problems, caused by the decreased oxide thickness and increasing doping levels in scaled technologies [5]. The ESD problems are further aggravated by the tight design window for high-performance I/O circuits, not allowing large ESD devices to be used as protection elements [6]. This ends up reducing the number of options available to an I/O designer [7]. ESD reliability imposes the following constraints over I/O design [7]:

- granularity in width and fixed length, which are imposed by some of the ESD rules, causing a tradeoff between the speed, area, and ESD performance of the I/O circuit;

- ESD diode termination, which affects the I/O signal integrity because of large overshoots and undershoots of I/O voltage.

Therefore, the overall I/O performance depends on how the I/O devices are designed and optimized while considering their susceptibility to ESD protection.

Previously, mixed-signal SoC products were designed using bipolar-CMOS-DMOS (BCD) technologies [8], [9]. The trend toward lowering the system cost has favored the use of a low-cost CMOS process. It was shown that a high-voltage (HV) CMOS process can be accomplished without any additional process complexity of buried layers as in the BCD process [10]. Scaling the HV CMOS process down to the  $0.13-\mu m$  node has recently been reported [11]. The published work also reports replacing the BCD process with a CMOS process in some applications that were previously dominated by the BCD technology.

HV or I/O devices are used in various applications such as broadband communication, mobile chips, smart power ICs, nonvolatile memories, microelectromechanical systems (MEMSs), etc. For high-speed data transfer on a twisted-pair copper connection, a subscriber line interface circuit integrated in CMOS technology is required [12]–[14]. Power management modules such as the high-efficiency switch-mode dc-dc converter are critical building blocks for state-of-the-art portable applications. They are used to accurately transform a battery supply into various regulated voltages, as required by their loads [15], [16]. Charge pump circuits are used to generate dc voltages higher than the nominal power supply [17], which are used in nonvolatile flash memories [18] and MEMS [19] applications. Charge pump circuits are also used in some low-voltage

analog designs to improve the circuit performance [20]. Some other applications are low-voltage-to-HV level shifters [21] and RF power amplifiers [22]. In Part I of this paper, three types of HV I/O transistors in 130-nm CMOS technology are realized, and their performance is compared for analog/RF applications.

Part I of this paper is organized as follows. Section II will review various HV devices in CMOS technology. Section III will discuss the device realization and simulation setup, whereas Section IV will describe the intrinsic behavior and impact of process variations/misalignments over the intrinsic performance of realized devices. The analog/RF performance of the various I/O devices is compared in Section V, followed by a discussion and summary of important findings in Section VI.

### II. HV DEVICES COMPATIBLE TO CMOS TECHNOLOGY

Conventional MOS transistors are generally not useful for HV or I/O applications. They are designed to process information (data) by using minimum energy and the least area. The maximum drain voltage is limited by the gate oxide breakdown, avalanche breakdown, and punchthrough. This forces a change in device geometry for devices that handle HV or I/O applications [23]. Various ways of achieving HV devices in CMOS technologies are listed as follows.

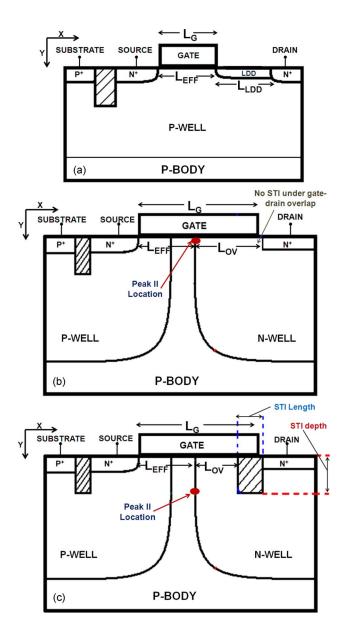

- 1) Lightly doped drain MOS (LDDMOS): By incorporating a lightly doped (n<sup>-</sup>/p<sup>-</sup>) drain (LDD) region between the drain  $(n^+/p^+)$  and the gate, as shown in Fig. 1(a), a high-drain-voltage operation can be achieved without exceeding the silicon critical electric field. The positive charge in the depleted LDD region (NMOS) is balanced by a negative charge in the p-layer underneath the LDD region. This makes the electric field nearly uniform in the lateral direction, which helps in increasing the maximum drain bias  $(V_{DS})$  by simply increasing the length of the LDD region [24], [25]. This action is called reduced surface field (RESURF) [26], [27]. The drawback of this approach is increased resistance in the ON-state and the requirement of an additional mask [23]. It is worth mentioning that the LDD or RESURF implant and the silicide-blocking mask exist in sub-100-nm-node CMOS technologies. Increasing the LDD length linearly improves (increases) the junction breakdown voltage but leads to a degraded ON resistance  $(R_{ON})$  and vice versa. This approach maintains a similar  $R_{\rm ON}.V_{\rm BD}$  tradeoff. It should be noted down that the LDD region implant is different (in terms of the doping profile and the junction depth) from the source/drain (S/D) extension implant in a standard (sub-100-nm-node) CMOS process.

- 2) Drain-extended MOS (DeMOS): Since advanced processes have both n-well and p-well implants, the RESURF action can be achieved by using deep n-well (NMOS) underneath the drain (n+) region, as shown in Fig. 1(b). Gate overlap is used to suppress the junction field in the ON-state [23]. The disadvantage of DeMOS is the change in gate-to-drain field profile, but it saves a mask and an implant step, which was previously required for the RESURF implant. In this paper, this device

Fig. 1. Schematics of I/O devices. (a) LDDMOS. (b) Non-STI DeMOS. (c) STI DeMOS.

is named as a non-shallow-trench-isolation (non-STI) DeMOS device. The gate overlap length (from the well junction to the drain edge) directly affects the breakdown voltage. Increasing the gate overlap length significantly improves the junction breakdown voltage, whereas it linearly degrades the ON resistance, eventually leading to an improved  $R_{\rm ON}.V_{\rm BD}$  tradeoff. At the same time, increasing the overlap length causes an unwanted area overhead and a gate-to-drain capacitance.

3) Shallow trench isolation (STI) DeMOS: A high gate oxide field in DeMOS devices near the gate-to-n-well (NMOS) overlap region requires a thick oxide underneath the gate-drain overlap. This is achieved by the local-oxidation-of-silicon (LOCOS) technology, although it decreases the device density. Furthermore, hot-carrier trapping in these devices leads to an undesirable shift in electrical characteristics [28], [29]. In more recent technologies, STI has been used to create a thick-oxide

| Devices      | L <sub>G</sub> (nm) | L <sub>EFF</sub> (nm) | $L_{OV}/L_{LDD}$ (nm) | STI Length (nm) |

|--------------|---------------------|-----------------------|-----------------------|-----------------|

| STI DeMOS    | 900                 | 390                   | 310                   | 200             |

| NonSTI DeMOS | 900                 | 420                   | 480                   | -               |

| LDDMOS       | 250                 | 250                   | 700                   | -               |

TABLE I

DIMENSIONAL SPECIFICATIONS OF OPTIMIZED DEVICES

region, as shown in Fig. 1(c) [30], [31]. This helps in increasing the logic density by eliminating the LOCOS bird's beak, but it has a negative effect on I/O devices because of the abrupt transition introduced to the ON-state current flow [23]. It is worth to mention here that, at present, most of the HV CMOS technologies use the LDDMOS devices. The overlap length (from the well junction to the STI edge) significantly affects the ON resistance and the junction breakdown voltage. Increasing the overlap length (by keeping other dimensional parameters unchanged) up to 200 nm improves the ON resistance and reduces the breakdown voltage, whereas it shows no change after 200 nm (this length depends on the n-well profile and, eventually, on the technology node). A change in overlap length does not affect the electric field in the oxide near the drain electrode because of the STI underneath drain-to-gate edge.

Furthermore, it is worth mentioning here that the junction breakdown voltage also depends on the p-well, the n-well/LDD profile, and the spacing between p-well and n-well/LDD regions.

In Part II, we have proposed a modified HV device structure and shown its performance improvement over STI DeMOS and DeMOS (non-STI DeMOS) in terms of analog/RF behavior and hot-carrier reliability. All 2-D simulations have been carried out using the well-calibrated Sentaurus technology computer-aided design (TCAD) tool. The Sprocess process simulator was used for simulating device structures, and the Sdevice tool was used for device simulations [32], [33].

### III. DEVICE REALIZATION AND SIMULATION SETUP

The devices used in this paper are realized using a well-calibrated process simulation deck. The same process flow is used for STI DeMOS and non-STI DeMOS transistors. This process is the same as the process flow of a conventional CMOS transistor, except for the  $\rm n^+$  drain, which is formed in the n-well region, and the  $\rm n^+$  source, which is formed in the p-well region. No  $V_T$  or punchthrough implant is used, and the threshold voltage of the device is adjusted by the p-well underneath the gate. Non-STI DeMOS does not have any STI in the n-well region underneath the gate–drain overlap. In these devices, the p-well underneath the source and gate acts like a single halo [34], which improves the subthreshold behavior.

The process flow for LDDMOS is the same as that for conventional CMOS, except for a large LDD region between the drain and the gate, which is used to increase the maximum drain voltage. It is required to protect the LDD region from n<sup>+</sup> S/D implant and silicidation (called silicide-blocking mask). The deep n-well and p-well have a retrograde profile, which is used to improve the breakdown characteristics of the device

TABLE II

ELECTRICAL SPECIFICATIONS OF OPTIMIZED DEVICES

| Devices      | I <sub>ON</sub> | I <sub>OFF</sub> | $V_{\mathbf{T}}$ | $V_{BD}$ |

|--------------|-----------------|------------------|------------------|----------|

| STI DeMOS    | 590 μA/μm       | 1nA/μm           | 0.3V             | 23V      |

| NonSTI DeMOS | 590 μA/μm       | 1nA/μm           | 0.3V             | 23V      |

| LDDMOS       | 590 μA/μm       | 1nA/μm           | 0.3V             | 13V      |

[35]. Implant parameters such as dose, energy, and tilt angle are calibrated to match the doping profiles extracted from secondary-ion mass-spectrometry (SIMS) measurement (SIMS plot not shown here). The gate oxide thickness (2.2 nm), spacer thickness, polysilicon height, STI depth (350 nm), etc., are kept as per the technology specification at 130-nm node. The n-well-to-p-well spacing, mask gate length, effective gate length, STI length, and gate overlap (listed in Table I) were optimized to achieve maximum  $I_{\rm ON}/I_{\rm OFF}$  and breakdown voltage. The achieved  $I_{\rm ON}$ ,  $I_{\rm OFF}$ ,  $V_T$ , and  $V_{\rm BD}$  are given in Table II.

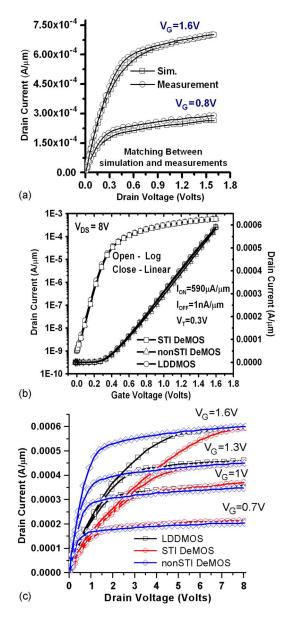

All three realized devices are optimized for maximum breakdown voltage by keeping the same  $I_{ON}$ ,  $I_{OFF}$ , and  $V_T$ . The effective channel length  $(L_{\rm EFF})$ , LDD length  $(L_{\rm LDD})$ or n-well-to-gate overlap  $(L_{OV})$ , and n-well-to-p-well spacing of the devices are calibrated to achieve matched  $I_D$ - $V_G$ characteristics. These devices are used to compare the breakdown, analog/RF performance, and scaling trends in this paper. A well-calibrated drift diffusion device simulation deck was used in this paper [33]. To study the breakdown characteristics of the device, a well-calibrated "New University of Bologna" (UniBo2) impact ionization model is used [36]. Carrier–carrier scattering is incorporated in the mobility model. Excess carrier recombination can take place via the Auger and Shockley-Read-Hall (SRH) recombination models. To incorporate this effect, the SRH and Auger recombination models are used. To take surface quantization effects into account, Van Dort's model is used for device simulation. Fig. 2(a) shows an excellent match between the experimental and simulated I-V characteristics of an NMOS device realized at the same technology node.

### IV. INTRINSIC PERFORMANCE OF THE DEVICES

# A. DC Characteristics

Fig. 2(b) shows the  $I_D$ – $V_G$  plot for all the three realized devices under an equal  $V_{\rm DS}$  voltage of 8 V. It is clear from the figure that all three devices have matched  $I_D$ – $V_G$  characteristics. An  $I_{\rm ON}$  value equal to 590  $\mu{\rm A}/\mu{\rm m}$ , an  $I_{\rm OFF}$  value equal to 1 nA/ $\mu{\rm m}$ , and a  $V_T$  of 0.3 V are achieved.

Fig. 2(c) shows the  $I_D$ – $V_D$  characteristics of all three devices at different gate voltages. The saturation characteristics of these devices are quite different because of their nonidentical drift regions, which leads to different drain resistance values. Non-STI DeMOS shows the best saturation characteristics and the lowest ON resistance ( $R_{\rm ON}$ ), whereas STI DeMOS shows the

Fig. 2. (a) Matching between simulated and experimental characteristics of the reference device. (b) Device characteristics:  $I_D$ – $V_G$ . All three devices have matched  $I_D$ – $V_G$  characteristics. (c) Simulated  $I_D$ – $V_D$  characteristics.

worst saturation characteristics and the highest  $R_{\rm ON}$  at maximum gate bias. LDDMOS shows moderate performance.

Fig. 3 shows the breakdown characteristics of all three devices. The  $I_D$ – $V_D$  plot is simulated with the impact ionization model turned on at  $V_{\rm GS}=0$  V. The breakdown voltage is taken as the drain voltage at which the drain current rises to ten times the nominal current, i.e.,  $10~{\rm nA}/\mu{\rm m}$ . STI DeMOS and non-STI DeMOS have an equal breakdown voltage of 23 V. It should be mentioned here that, to achieve an equal  $I_{\rm ON}$ , the effective channel length of STI DeMOS was kept slightly lower than that of non-STI DeMOS. The difference is, however, not too high, as can be seen from the comparable breakdown voltages between these two devices. LDDMOS has a lower breakdown voltage, because of the shallow LDD region and shorter channel length as compared to DeMOS devices. Although the breakdown voltages of STI and non-STI DeMOS devices are comparable: 1) the dependence of the breakdown

Fig. 3. Breakdown characteristics of the realized I/O devices  $(I_D - V_D$  curve at  $V_G = 0~\rm{V}).$  The plot shows that the DeMOS has a higher  $V_{\rm{BD}}$  compared to the LDDMOS.

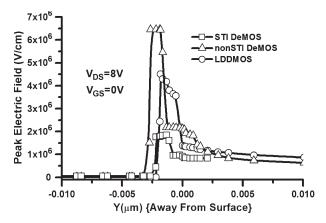

Fig. 4. Peak electric field across the gate oxide of I/O devices. Non-STI DeMOS has a higher field compared to STI DeMOS and LDDMOS.

voltage on the gate-to-n-well overlap length  $(L_{\rm OV})$  is different for both devices and 2) the location of the impact ionization peak (i.e., peak electric field at the n-well-p-well junction) and its 2-D profile are different for both the STI and non-STI devices [as shown in Fig. 1(b) and (c)]. For STI DeMOS, it exists deep inside the bulk (300 nm below the surface), whereas for non-STI DeMOS, it exists closer to the surface. It is worth mentioning here that the threshold voltage of LDDMOS was optimized by using a  $V_T$  adjust implant (high doping in the channel), which leads to lower channel mobility. However, the p-well in DeMOS devices acts like a single halo, which results in a larger portion of the channel being lightly doped, giving rise to a significant improvement in channel mobility [34]. To achieve an equal  $I_{ON}$  for all three devices, the LDDMOS channel length is kept approximately four times lower than that of the DeMOS devices.

Fig. 4 shows the peak electric field across the gate oxide, which was extracted near the gate-to-drain edge in the overlap region. The electric field in non-STI DeMOS is three times higher than that in STI DeMOS, which shows that non-STI DeMOS is highly prone to a gate oxide breakdown. This may also lead to a gate oxide failure before junction breakdown in non-STI DeMOS. The reduced gate oxide field in STI DeMOS is because of the STI underneath the gate—drain overlap region

Fig. 5. Impact of process variability over intrinsic performance of STI DeMOS. (a)  $R_{\rm ON}$ . (b) Breakdown voltage. (c)  $I_{\rm OFF}$ . (d)  $I_{\rm ON}$ .

(spacer), which helps in relaxing the effective potential in the gate-to-n-well overlap region. Basically, the potential is more uniformly distributed in the n-well region, which was attributed to the STI underneath the gate-drain edge. This further helps in reducing the effective potential in the gate-to-n-well overlap region, which eventually leads to lower vertical electric fields. Incorporating the STI also leads to a slightly higher depletion in the gate-to-n-well overlap region, which further helps in reducing the lateral electric field near to the surface. A high gate oxide field also causes a significant increase in time-dependent dielectric breakdown and gate leakage [3], [37].

### B. Impact of Process Variation and Misalignment

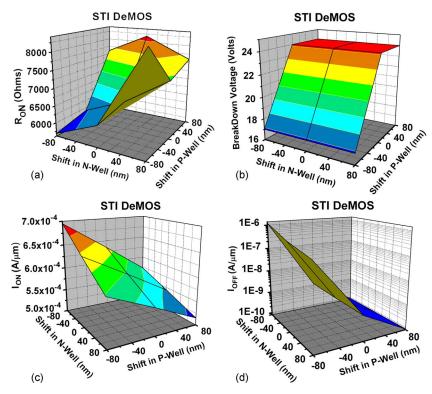

Variability in delay and power consumption in CMOS devices, circuits, and chips arises from process variations (or misalignment) in scaled technologies. The impact of process variations and misalignments such as variations in the STI length and n-well-to-p-well spacing on the important device parameters such as ON resistance  $(R_{\rm ON})$ ,  $I_{\rm ON}/I_{\rm OFF}$ , and breakdown voltages is discussed.

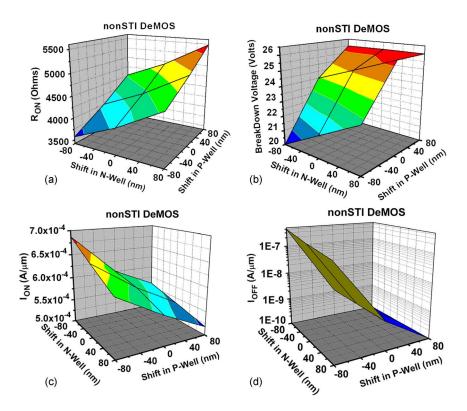

Figs. 5 and 6 show the impact of a shift or misalignment in a well edge (n-well and p-well) on  $R_{\rm ON}$ , the breakdown voltage,  $I_{\rm ON}$ , and  $I_{\rm OFF}$  for STI DeMOS and non-STI DeMOS. Fig. 5(a) shows the variation in  $R_{\rm ON}$ .  $R_{\rm ON}$  is measured at a  $V_D$  equal to 0.1 V. It is clear from Fig. 5(a) that, as the n-well and p-well edges shift in the positive direction (toward the drain), the ON resistance degrades (i.e., increases) and vice versa. A positive shift in n-well increases the effective channel length, eventually leading to a higher channel resistance. A positive shift in p-well increases the threshold voltage of the device, which causes a higher channel resistance. Fig. 5(b) shows the variation in breakdown voltage with respect to the shift in the n-well and

p-well edges. The breakdown voltage does not change with a positive shift in the p-well edge, whereas it reduces as it shifts toward the source because of the increase in the leakage current. The breakdown voltage does not change with variations in the n-well edge. Fig. 5(c) and (d) shows the variation in  $I_{\rm ON}$  and  $I_{\rm OFF}$  with respect to the shift in n-well and p-well edges. As the n-well and p-well shift towards the source side (i.e., negative direction),  $I_{\rm ON}$  and  $I_{\rm OFF}$  increases. A shift in n-well toward the source reduces the effective channel length, and a shift in p-well toward the source reduces the effective threshold voltage of the device, which leads to increased  $I_{\rm ON}$  and  $I_{\rm OFF}$ . Fig. 6 shows a similar trend for non-STI DeMOS. Relatively, non-STI DeMOS shows less sensitivity to edge variations as compared to STI DeMOS because of its larger effective channel length and the difference in its impact ionization profiles.

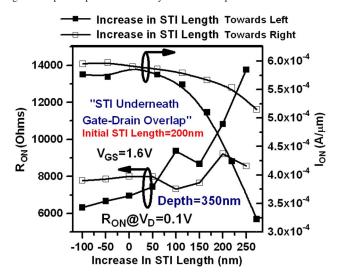

Fig. 7 shows the impact of variation in STI length on  $R_{\rm ON}$  and  $I_{\rm ON}$ . As the STI length increases toward the left (source side),  $R_{\rm ON}$  increases, and  $I_{\rm ON}$  decreases. The variation in  $I_{\rm ON}$  and  $R_{\rm ON}$  is less for +/-100 nm, but it is significant beyond +100 nm. Increasing the STI thickness toward the right (drain side) up to 100 nm first decreases and then increases the  $R_{\rm ON}$ . The increase in  $R_{\rm ON}$  beyond 100 nm is because of an increase in the drain resistance.  $I_{\rm ON}$  always decreases by increasing the STI thickness toward the right.

# V. ANALOG/RF PERFORMANCE COMPARISON OF THE DEVICES

## A. Analog Performance

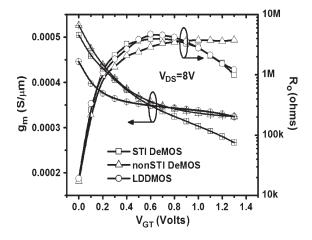

Fig. 8 shows the transconductance  $(g_m)$  and output resistance  $(R_O)$  of the simulated devices for a complete range of gate overdrive voltages. For a moderate gate overdrive

Fig. 6. Impact of process variability over intrinsic performance of non-STI DeMOS. (a)  $R_{\rm ON}$ . (b) Breakdown voltage. (c)  $I_{\rm OFF}$ . (d)  $I_{\rm ON}$ .

Fig. 7. Impact of variation in STI length over the turn-on behavior of a device.

voltage  $(V_{\rm GT} < 1~{\rm V})$ , the transconductance of these devices is comparable. More precisely, LDDMOS and STI DeMOS have a slightly higher transconductance, for a  $V_{\rm GT}$  below 1 V, as compared to non-STI DeMOS. At a higher gate overdrive voltage (i.e.,  $V_{\rm GT} > 1~{\rm V}$ ), non-STI DeMOS shows a significant improvement over the other two structures. Reduced draininduced barrier lowering and channel length modulation, because of the single-halo nature of STI and non-STI DeMOS structures, contribute to the significantly higher output resistance as compared to that of the LDDMOS device at a low  $V_{\rm GT}$ . Furthermore, the shorter channel lengths required for LDDMOS to achieve a  $I_{\rm ON}/I_{\rm OFF}$  equal to that of DeMOS devices cause a degradation in the output resistance. At a higher

Fig. 8. Variation in transconductance  $(g_m)$  and output resistance  $(R_O)$  of all the realized devices, as a function of the gate overdrive voltage.

gate overdrive voltage, STI DeMOS shows a significant degradation in output resistance because of the high drain resistance, which leads to deteriorated saturation characteristics.

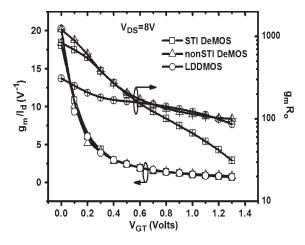

Performance parameters  $g_m/I_D$  and  $g_mR_O$  (intrinsic gain) of the device are also studied at a drain bias voltage of 8 V for a wide range of gate overdrive voltages, as shown in Fig. 9. Since the  $I_D$ – $V_G$  characteristics of all the three devices are matched for performance comparisons, the performance parameter  $g_m/I_D$  for all three devices is identical and does not show any difference in performance. The intrinsic gain  $(g_mR_O)$  plotted in Fig. 9 shows that the DeMOS devices consistently outperform the LDDMOS device for lower values of gate overdrive voltages. Good control of short-channel effects in DeMOS devices (because of the single-halo nature)

Fig. 9. Variation in performance parameters  $g_m/I_D$  and intrinsic gain  $(g_mR_O)$  of all the realized devices, as a function of the gate overdrive voltage.

Fig. 10. Impact of the substrate bias on the threshold voltage of the various I/O devices.

results in an increased  $g_m R_O$  value. For a higher value of gate overdrive voltage, STI DeMOS shows a significant reduction (about 500%) in intrinsic gain because of the degradation in transconductance and output resistance, as discussed earlier.

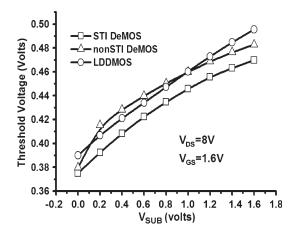

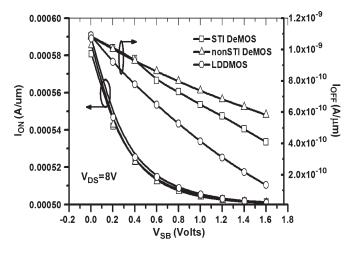

Figs. 10 and 11 show the effect of the body bias on the device intrinsic performance. The threshold voltage,  $I_{\rm ON}$ , and  $I_{\rm OFF}$  are plotted for a range of body bias voltages in Figs. 10 and 11. It shows that all three devices exhibit similar substrate bias sensitivity. Fig. 11 shows that the reduction in  $I_{\rm OFF}$  for LDDMOS is higher as compared to that for DeMOS devices, whereas the change in  $I_{\rm ON}$  with respect to the substrate bias is similar for all three devices.

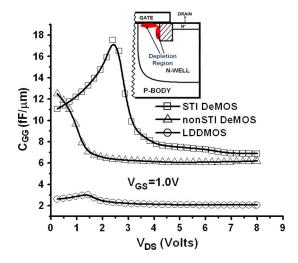

Fig. 12 shows the overall gate capacitance  $(C_{\rm GG})$ , which includes the gate oxide capacitance  $(C_{\rm OX})$ , overlap, and parasitic capacitance seen by the gate terminal, as a function of the drain bias. The  $C_{\rm GG}$  for LDDMOS is constant throughout the drain bias range and is significantly lower (by about three times) as compared to that for DeMOS devices. As we discussed earlier, the drawn channel length for LDDMOS is four times less as compared to that for DeMOS devices, which leads to a lower value of  $C_{\rm GG}$ . At a lower value of  $V_D$ , STI DeMOS shows a nonlinear behavior:  $C_{\rm GG}$  first increases to a higher value, and then, it decreases. This behavior is attributed to the extra parasitic capacitance because of the depletion region around the

Fig. 11. Impact of substrate bias on the intrinsic performance of the realized I/O devices. The plot shows the variation in  $I_{\rm ON}$  and  $I_{\rm OFF}$  of all the realized I/O devices as a function of the substrate bias.

Fig. 12. Parasitic behavior of the I/O devices. The plot shows the gate-to-gate capacitance  $(C_{\rm GG})$ , which is the sum of gate oxide capacitance and parasitic capacitance seen by the gate terminal, as a function of the drain bias.

STI and under the gate overlap. Since the depletion width of the depleted region across the STI and under the gate overlap depends on the gate and drain biases,  $C_{\rm GG}$  shows a nonlinear characteristic. In Part II, we will show that this nonlinear nature gets suppressed by scaling the STI depth or, eventually, by reducing the total depletion area. For a higher drain bias, the  $C_{\rm GG}$  value for STI DeMOS is 10% higher as compared to that for non-STI DeMOS.

# B. Impact of Scaling on the Device Performance

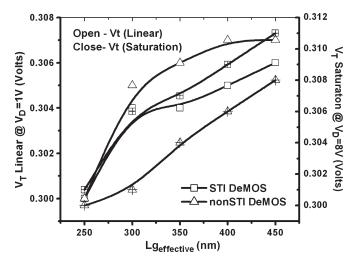

Fig. 13 shows the  $V_T$  roll-off for DeMOS devices. The variation in linear  $V_T$  and saturation  $V_T$  is plotted with respect to the effective channel length of the devices. The  $V_T$  roll-off shows the same trend for both devices. There is a less than 1% variation in linear and saturation  $V_T$ , for a reduction in effective channel length from 450 to 250 nm. The effective channel length is reduced by shifting the n-well edge toward the source by keeping the rest of the process parameters identical. The negligible roll-off has been attributed to the single-halo

Fig. 13. Impact of scaling on the threshold voltage of DeMOS devices. The plot shows the linear and saturation threshold voltage of STI DeMOS and non-STI DeMOS as a function of the channel length.

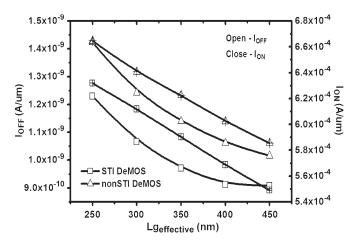

Fig. 14. Impact of scaling on the subthreshold behavior of DeMOS devices. The plot shows the  $I_{\rm ON}$  and  $I_{\rm OFF}$  of STI DeMOS and non-STI DeMOS as a function of the channel length.

nature of the DeMOS device, where the source is surrounded by a p-well that protects it from short-channel effects.

$I_{\rm ON}$  and  $I_{\rm OFF}$  are plotted in Fig. 14 with respect to the effective channel length. The figure shows that the DeMOS devices are not prone to short-channel effects and that there is no significant rise in leakage current for a reduced channel length. The  $I_{\rm ON}$  for non-STI DeMOS is always higher than that for STI DeMOS for any effective channel length because of the reduced drain resistance in non-STI DeMOS, as discussed earlier.

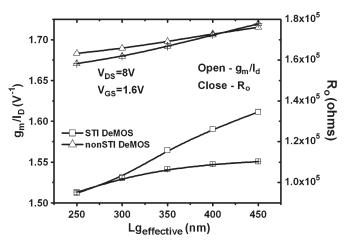

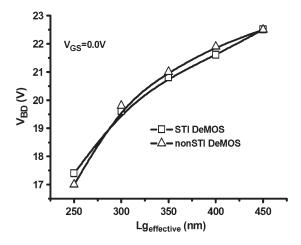

Fig. 15 shows the roll-off in performance parameters  ${\rm g}_m/I_D$  and  $R_O$  with respect to the channel length. Because of the single-halo nature of the device, the degradation in performance parameters is not significant. Furthermore, it is clear from the figure that non-STI DeMOS always shows an improved performance over STI DeMOS for a range of effective channel length values. However, one needs to consider the degradation in breakdown voltage because of the reduced effective channel lengths. Fig. 16 shows that the breakdown voltage is reduced from 23 to 17 V for a reduction in effective channel length from 450 to 250 nm, which is still acceptable for I/O applications.

Fig. 15. Impact of scaling on the analog/RF performance of STI DeMOS and non-STI DeMOS. The plot shows the performance parameters  ${\bf g}_m/I_D$  and  $R_O$  as a function of the channel length.

Fig. 16. Impact of scaling on the breakdown voltage of STI DeMOS and non-STI DeMOS.

### VI. CONCLUSION

In this paper, three optimized I/O devices, namely, the LDDMOS, STI DeMOS, and non-STI DeMOS devices, have systematically been compared using an extensive TCAD-based framework. LDDMOS (RESURF device), which is widely in use, shows moderate performance as compared to other two devices but exhibits a very low breakdown voltage and severe gate oxide reliability issues in scaled technology nodes. Non-STI DeMOS has a higher breakdown voltage as compared to that of LDDMOS and shows improved analog/RF performance over the other two devices but suffers from the worst gate oxide reliability. Incorporating an STI region underneath the gate-drain overlap suppresses the peak gate oxide electric field, but it significantly increases the drain resistance, which eventually degrades the saturation and turn-on characteristics of the device. This causes the degraded analog performance of STI DeMOS as compared to that of the other two devices. The single-halo nature of DeMOS devices improves the scalability of these devices and also suppresses the short-channel effects. Since STI DeMOS has a less effective channel length as compared to non-STI DeMOS, for the same  $I_{ON}$  and  $I_{OFF}$ , it

| FIELDS                      | STI DeMOS | NonSTI DeMOS | LDDMOS |

|-----------------------------|-----------|--------------|--------|

| Breakdown Voltage           | Н         | Н            | L      |

| Oxide Elec. Field           | L         | Н            | M      |

| $G_{\mathbf{m}}$            | L         | Н            | L      |

| $R_{O}$                     | L         | Н            | Н      |

| Intrinsic Gain              | L         | H            | M      |

| Sub. Bias Sensitivity       | L         | L            | L      |

| Scalability                 | H         | H            | -      |

| Parasitic Capacitance       | Н         | M            | M      |

| (Normalized with gate area) |           |              |        |

| Parasitic Capacitance (Abs) | Н         | M            | L      |

TABLE III

PERFORMANCE COMPARISON OF REALIZED DEVICES

H-High M-Moderate L-Low

has a higher sensitivity to process variations. The performance characteristics of all these devices are summarized in Table III.

In the second part of this paper, we have shown further optimization of the STI DeMOS to achieve analog/RF performance similar to that of non-STI DeMOS without sacrificing on the gate oxide and hot-carrier injection reliability advantages of these devices.

#### ACKNOWLEDGMENT

The authors would like to thank Synopsis for the Sentaurus licenses.

### REFERENCES

- S. Voldman, "ESD protection in a mixed voltage interface and multirail disconnected power grid environment in 0.5- and 0.25-um channel length CMOS technology," in *Proc. EOS/ESD Symp.*, 1994, pp. 125–134.

- [2] M.-D. Ker and K.-H. Lin, "Overview on electrostatic discharge protection design for mixed-voltage I/O interfaces: Design concept and circuit implementations," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 2, pp. 235–246, Feb. 2006.

- [3] T. Furukawa, D. Turner, S. Mittl, M. Maloney, R. Serafin, W. Clark, J. Bialas, L. Longenbach, and J. Howard, "Accelerated gate-oxide breakdown in mixed-voltage I/O circuits," in *Proc. IEEE IRPS*, 1997, pp. 169–173.

- [4] E. Takeda and N. Suzuki, "An empirical model for device degradation due to hot-carrier injection," *IEEE Electron Device Lett.*, vol. EDL-4, no. 4, pp. 111–113, Apr. 1983.

- [5] A. Amerasekera, V. Gupta, K. Vasanth, and S. Ramaswamy, "Analysis of snapback behavior on the ESD capability of sub-20 um NMOS," in *Proc. IRPS*, 1999, pp. 159–166.

- [6] M. Radhakrishnan, V. Vassilev, B. Keppens, V. De Heyn, M. Natarajan, and G. Groeseneken, "ESD reliability issues in RF CMOS circuits," in *Proc. IWPSD*, Dec. 2001, pp. 551–556.

- [7] S. Dabral and T. Maloney, Basic ESD and I/O Design. New York: Wiley, 1998

- [8] A. Moscatelli, A. Merline, G. Croce, P. Galbiati, and C. Contiero, "LDMOS implementation in a 0.35 mm BCD technology (BCD6)," in *Proc. ISPSD*, Toulouse, France, 2000, pp. 323–326.

- [9] C. Contiero, B. Murari, and B. Vigna, "Progress in power ICs and MEMs, analog technologies to interface to the real world," in *Proc. ISPSD*, Kitakyushu, Japan, 2004, pp. 3–12.

- [10] N. J. Rohrer, "Introduction for statistical variation and techniques for design optimization," presented at the Int. Solid-State Circuits Conf. (ISSCC), San Francisco, CA, 2006, Tutorial.

- [11] C. Grelu, N. Baboux, R. A. Bianchi, and C. Plossu, "Switching loss optimization of 20 V devices integrated in a 0.13 μm CMOS technology for portable applications," in *Proc. Int. Symp. Power Semicond. Devices ICs*, Santa Barba, CA, 2005, pp. 339–342.

- [12] M. Vahidfar, A. Tajalli, and M. Atarodi, "A low-power subscriber line interface circuit in a high-voltage CMOS technology," in *Proc. IEEE ISCAS*, 2002, vol. 5, pp. 409–412.

- [13] K. K. Ghosh and C. A. T. Salama, "A high voltage CMOS ADSL line driver," in *Proc. IEEE 15th ISPSD*, Apr. 14–17, 2003, pp. 105–108.

- [14] A. Tajalli and S. Mojtaba Atarodi, "Structured design of an integrated subscriber line interface system and circuit," in *Proc. ISCAS*, May 2003, vol. 2, pp. II-284–II-287.

- [15] C. F. Lee and P. K. T. Mok, "A monolithic current-mode CMOS DC-DC converter with on-chip current-sensing technique," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 3–14, Jan. 2004.

- [16] R. D. Middlebrook, "Small-signal modeling of pulse-width modulated switching-mode power converters," *Proc. IEEE*, vol. 76, no. 4, pp. 343– 354, Apr. 1988.

- [17] M.-D. Ker and S.-L. Chen, "Ultra high voltage charge pump circuit in low voltage bulk CMOS processes with polysilicon diodes," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 54, no. 1, pp. 47–51, Jan. 2007.

- [18] T. Tanzawa, Y. Takano, K. Watanabe, and S. Atsumi, "High-voltage transistor scaling circuit techniques for high-density negative-gate channel-erasing NOR flash memory," *IEEE J. Solid-State Circuits*, vol. 37, no. 10, pp. 1318–1325, Oct. 2002.

- [19] M. R. Hoque, T. McNutt, J. Zhang, A. Mantooth, and M. Mojarradi, "A high voltage Dickson charge pump in SOI CMOS," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2003, pp. 493–496.

- [20] J. S. Wang, H.-Y. Li, C. Yeh, and T.-F. Chen, "Design technique for single-low-VDD CMOS systems," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1157–1165, May 2005.

- [21] J. Rocha, M. Santos, J. M. D. Costa, and F. Lima, "High voltage tolerant level shifters and DCVSL in standard low voltage CMOS technologies," in *Proc. IEEE ISIE*, Jun. 2007, pp. 775–780.

- [22] P. Leroux, V. Vassilev, M. Steyaert, and H. Maes, "High ESD performance, low power CMOS LNA for GPS applications," *J. Electrostat.*, vol. 59, no. 3/4, pp. 179–192, Oct. 2003.

- [23] P. Hower, S. Pendharkar, and J. Smith, "Integrating power devices into silicon roadmaps," *Proc. Inst. Elect. Eng.—Circuits, Devices Syst.*, vol. 153, no. 1, pp. 73–78, Feb. 2006.

- [24] M. Vermandel, C. De Backere, A. Van Calster, J. Witters, and M. Tack, "A high voltage p-type drain extended MOS in a low voltage sub-micron CMOS technology," in *Proc. 28th Eur. Solid-State Device Res. Conf.*, Sep. 1998, pp. 492–495.

- [25] T. Efland, T. Keller, S. Keller, and J. Rodriguez, "Optimized complementary 40 V power LDMOS-FETs use existing fabrication steps in submicron CMOS technology," in *IEDM Tech. Dig.*, Dec. 1994, pp. 399–402.

- [26] J. Apels, H. Vaes, and J. Verhoeven, "High voltage thin layer devices (RESURF devices)," in *IEDM Tech. Dig.*, 1979, pp. 238–241.

- [27] M. Imam, M. Quddus, J. Adams, and Z. Hossain, "Efficacy of charge sharing in reshaping the surface electric field in high-voltage lateral RESURF devices," *IEEE Trans. Electron Devices*, vol. 51, no. 1, pp. 141–148, Jan. 2004.

- [28] S. Pendharkar, R. Higgins, T. Debolske, T. Efland, and B. Nehrer, "Optimization of low voltage n-channel LDMOS devices to achieve required electrical and lifetime SOA," in *Proc. ISPSD*, Santa Fe, NM, 2002, pp. 261–264.

- [29] P. Moens, M. Tack, R. Degraeve, and G. Groeseneken, "A novel hot-hole injection degradation model for lateral nDMOS transistors," in *IEDM Tech. Dig.*, 2001, pp. 877–880.

- [30] A. Brand, "Transistor device configurations for high voltage applications and improved device performance," U.S. Patent 6 287 908, Sep. 11, 2001.

- [31] A. Brand, "Transistor device configurations for high voltage applications and improved device performance," U.S. Patent 6 172 401, Jan. 9, 2001.

- [32] Sentaurus Sprocess, ver. Z-2007.03, Mar. 2007.

- [33] Sentaurus Device User Guide, Synopsys, Inc., Mountain View, CA, Mar. 2007, ver. Z-2007.03.

- [34] K. Narasimhulu, D. K. Sharma, and V. R. Rao, "Impact of lateral asymmetric channel doping on deep submicrometer mixed-signal device and circuit performance," *IEEE Trans. Electron Devices*, vol. 50, no. 12, pp. 2481–2489, Dec. 2003.

- [35] S. H. Voldman, "A review of electrostatic discharge (ESD) in advanced semiconductor technology," *Microelectron. Reliab.*, vol. 44, no. 1, pp. 33– 46, Jan. 2004.

- [36] S. Reggiani, M. Rudan, E. Gnani, and G. Baccarani, "Investigation about the high-temperature impact-ionization coefficient in silicon," in *Proc. 34th ESSDERC*, 2004, pp. 245–248.

[37] W. Chen and T.-P. Ma, "Oxide charge buildup and spread-out dur-

- [37] W. Chen and T.-P. Ma, "Oxide charge buildup and spread-out during channel-hot-carrier injection in NMOSFETs," *IEEE Electron Device Lett.*, vol. 13, no. 6, pp. 319–321, Jun. 1992.

Mayank Shrivastava (S'09) was born in Lucknow, India, in 1984. He received the B.S. degree in engineering from Rajiv Gandhi Technical University, Bhopal, India, in 2006. He is currently working toward the Ph.D. degree with the Center for Excelence in Nanoelectronics, Department of Electrical Engineering, Indian Institute of Technology (IIT) Bombay, Mumbai, India

In July 2006, he joined IIT Bombay as a Research Fellow. He was a Visiting Research Scholar with Infineon Technology AG, Munich, Germany, from

April 2008 to October 2008. His current research interest includes ESD- and HCD-aware I/O device design, ESD-aware technology development, FinFET and UTB-Planar SOI devices, nonvolatile analog memories, and electrothermal modeling and simulation. He is the holder of five U.S. patents and one Indian patent pending in the fields of ESD, I/O devices, FinFETs, and nonvolatile analog memory.

Mr. Shrivastava was a recipient of the Intel's 2008 Asia Academic Forum (AAF'08) Best Research Paper Award in the circuit design category. He also served as a Reviewer for the IEEE Transactions on Electron Devices, the 2009 IEEE International Electron Devices Meeting (IEDM'09), and the 2010 International Conference on VLSI Design (VLSI'10).

Maryam Shojaei Baghini (M'00–SM'09) received M.S. and Ph.D. degrees in electrical engineering from Sharif University of Technology, Tehran, Iran, in 1991 and 1999, respectively.

In 1991 and 1992, she was with the Saff and Kavoshgaran Companies, working on the design and test of custom and semicustom ICs. From 1999 to 2000, she was with the Emad Semiconductor Company as a Senior Analog IC Design Engineer. In 2001, she joined the Indian Institute of Technology (IIT) Bombay, Mumbai, India, as a Postdoctoral

Fellow and is currently a faculty member with the Center for Excellence in Nanoelectronics, Department of Electrical Engineering. As a part of her research in IIT Bombay, she has designed one of the most power-efficient CMOS instrumentation ampli?ers for biomedical applications in 2004. She is a member of the research group on "Device Circuit Interaction in Emerging Technologies" in IIT Bombay. The outcomes of this group have been published in IEEE journals and conferences and also submitted as patent applications. She has been the designer or a codesigner of several analog chips in the industry and academia. She is the author or a coauthor of 45 international journal and conference papers and the author of one invited book chapter. She is the holder or a coholder of seven patent applications. Her current research interests include device-circuit interaction in emerging technologies, high-performance analog/mixed-signal/RF VLSI design and test, analog/mixed-signal/RF modeling and EDA, power management for system-on-chip applications, high-speed interconnects, analog aspects of digital circuits, and circuit design with organic thin-film components.

Dr. Shojaei Baghini is a corecipient of the Best Research Award in circuit design at the Intel Corporation 2008 Asia Academic Forum (AAF'08) and the Third Award on research and development at the Fifteenth International Festival of Kharazmi in 2002. Her team of students won in the first Cadence Design Systems, Inc., Student Design Contest, among South Asian Association for Regional Cooperation countries, in 2006.

**Harald Gossner** (M'06) received the Dipl.Phys. degree from the Ludwig-Maximilians University, Munich, Germany, in 1990 and the Ph.D. degree in electrical engineering from the Universität der Bundeswehr, Munich, Germany, in 1995.

Since 1995, he has been with Infineon Technologies AG, Munich, Germany, working on the development of ESD protection concepts for bipolar, BiCMOS, and CMOS technologies. He is the Head of the team of Infineon's Center of Competence for ESD and External Latchup Development and also a

Senior Principal who guides the company activities in the field of overvoltage robust design. He is the author or a coauthor of more than 40 technical papers and one book in the field of ESD.

Dr. Gossner is a member of the management board of the International ESD Workshop (IEW) and a Cochair of the Industry Council on ESD Target Values. He is serving in the technical program committee of the EOS/ESD Symposium, the IEEE International Electron Devices Meeting (IEDM), and IEW.

**V. Ramgopal Rao** (M'98–SM'02) received the M.Tech. degree from the Indian Institute of Technology (IIT) Bombay, Mumbai, India, in 1991 and the Dr.Ing. degree from the Universitaet der Bundeswehr, Munich, Germany, in 1997.

He is currently a Professor with the Center for Excellence in Nanoelectronics, Department of Electrical Engineering, IIT Bombay. He is the author of more than 200 publications in refereed international journals and conference proceedings. He is the holder of three patents with eight patents currently

pending. His areas of interest include physics, technology, and characterization of silicon CMOS devices for logic and mixed-signal application and nanoelectronics.

Prof. Rao is a Fellow of the Indian National Academy of Engineering, the Indian Academy of Sciences, and the Institution of Electronics and Telecommunication Engineers. He received the Shanti Swarup Bhatnagar Prize in Engineering Sciences in 2005 for his work on electron devices. He also received the Swarnajayanti Fellowship Award for 2003-2004, which was instituted by the Department of Science and Technology, Government of India, the 2007 IBM Faculty Award, the 2008 "The Materials Research Society of India (MRSI) Superconductivity & Materials Science Prize," and the 2009 TechnoMentor Award instituted by the Indian Semiconductor Association. He is an Editor for the IEEE TRANSACTIONS ON ELECTRON DEVICES in the CMOS devices and technology area. He is a Distinguished Lecturer of the IEEE Electron Devices Society. He was the Organizing Committee Chair for the Seventeenth International Conference on VLSI Design and the Fourteenth International Workshop on the Physics of Semiconductor Devices and serves on the program/ organizing committees of various international conferences, including the International Electron Devices Meeting (IEDM), the IEEE Asian Solid-State Circuits Conference, the 2006 IEEE Conference on Nano-Networks, the ACM/IEEE International Symposium on Low Power Electronics and Design, and the Eleventh IEEE VLSI Design & Test Symposium, among others. He was the Chairman of the IEEE AP/ED Bombay Chapter during 2002-2003 and currently serves on the executive committee of the IEEE Bombay Section, in addition to being the Vice Chair of the IEEE Asia-Pacific Regions/Chapters Subcommittee.