# A Solution Toward the OFF-State Degradation in Drain-Extended MOS Device

Mayank Shrivastava, *Member, IEEE*, Ruchil Jain, Maryam Shojaei Baghini, *Senior Member, IEEE*, Harald Gossner, *Member, IEEE*, and V. Ramgopal Rao, *Senior Member, IEEE*

Abstract—We investigated the surface band-to-band tunnelling (BTBT) current under the OFF-state condition in drain-extended MOS (DeMOS) devices. We found significant gate-induced drain leakage current due to surface BTBT, which was also reported earlier as the dominant cause of early time-dependent dielectric breakdown and device failure. Furthermore, a layout solution for the existing DeMOS device is proposed in order to mitigate the surface BTBT current and the associated gate oxide reliability issues, without sacrificing the mixed-signal performance of the device.

Index Terms—Band-to-band tunnelling (BTBT), drain extended, drain-extended MOS (DeMOS), input/output, time-dependent dielectric breakdown (TDDB).

### I. Introduction

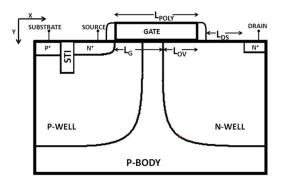

S THE TECHNOLOGY is shrinking below 45-nm node, the core circuits are now operating at voltages below 1 V, whereas the input/output circuits are still operating at higher voltages, leading to severe gate oxide reliability issues. This can either be due to hot-carrier degradation or electrostatic discharge events. There are several high-voltage structures proposed for advanced CMOS technology, and among them, drainextended MOS (DeMOS) device is one of the possible options due to its easy integration in the advanced CMOS process and its process compatibility. There are two possible DeMOS structures suitable for advanced CMOS technologies: 1) shallow trench isolation (STI) type, i.e., with an STI underneath a gateto-drain overlap, and 2) non-STI type, i.e., without any STI underneath a gate-to-drain overlap (as shown in Fig. 1). Although the STI-type DeMOS has shown excellent gate oxide reliability, it is known for its degraded mixed-signal performance [1], [2]. The non-STI device shows excellent mixed-signal performance but suffers from significant gate oxide reliability concerns in the OFF state [3]. As reported earlier [3], [4], significant surface band-to-band tunnelling (BTBT) current leads to excess hot-hole generation in the OFF state and causes the early

Manuscript received May 28, 2010; accepted September 21, 2010. Date of current version November 19, 2010. The review of this brief was arranged by Editor J. S. Suehle.

M. Shrivastava is with Infineon Technologies, East Fishkill, NY 12533 USA (email: shrivastva.mayank@gmail.com; Mayank.Shrivastava@infineon.com).

R. Jain is with Global Foundry Singapore Pvt. Ltd., Singapore 738406.

M. S. Baghini and V. R. Rao are with the Center for Excellence in Nanoelectronics, Department of Electrical Engineering, Indian Institute of Technology, Bombay, Mumbai 400076, India (email: rrao@ee.iitb.ac.in).

H. Gossner is with Infineon technologies AG, 81609 Munich, Germany (email: harald.gossner@infineon.com).

Color versions of one or more of the figures in this brief are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2010.2082549

Fig. 1. Non-STI-type DeMOS device. Standard device, which is prone to TDDB failure in the OFF state, has  $L_{\rm DS}=0$  nm.

time-dependent dielectric breakdown (TDDB) failure of the non-STI device. In this brief, we have proposed a modification in the device's layout, which mitigates the surface BTBT current and eventually helps in improving the associated gate oxide reliability behavior significantly without sacrificing its mixed-signal performance.

This brief is arranged as follows. Section II describes the experimental and simulation setup. The proposed modification and results are discussed in Section III, and Section IV summarizes the important contributions of this study.

## II. SIMULATION AND EXPERIMENTAL SETUP

A thin-gate-oxide non-STI-type DeMOS device was fabricated using standard 65-nm CMOS process and characterized. For simulation studies, the device was realized using a well-calibrated process simulation deck. The device simulation setup with well-calibrated mobility models for hydrodynamic transport was used.

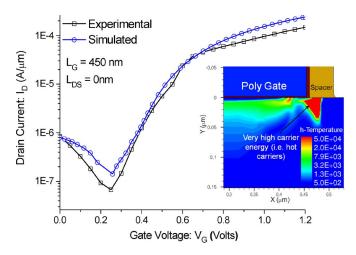

In order to accurately capture the surface BTBT current and carrier energy (or temperature), Hurkx BTBT model [5] was calibrated with the reference non-STI-type DeMOS device, and carrier (i.e., both electron and hole) temperatures were solved in the hydrodynamic simulations. Fig. 2(a) shows the calibration of our simulation setup with experiments. This simulation setup is used further in order to study the performance of the modified device.

# III. RESULTS AND DISCUSSIONS

Fig. 2 shows the experimental and simulated  $I_D$ – $V_G$  characteristics of the non-STI DeMOS device (with  $L_G=450$  nm). The inset in Fig. 2 shows the hole temperature  $(T_h)$  profile

Fig. 2. Experimental and simulated  $I_D$ – $V_G$  characteristics (@  $V_D=5$  V) of standard DeMOS device (i.e.,  $L_{\rm DS}=0$  nm). Inset shows the hole temperature (in kelvins) contour extracted from hydrodynamic simulations in the OFF state (i.e.,  $V_D=5$  V and  $V_G=0$  V).

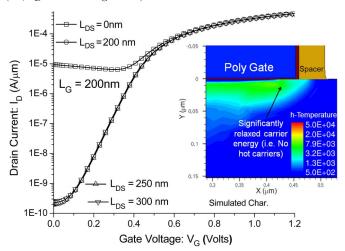

Fig. 3. Simulated  $I_D$ – $V_G$  characteristics (@  $V_D$  = 5 V) of the modified DeMOS device (i.e.,  $L_{\rm DS} \geq 200$  nm). Inset shows significantly relaxed hole temperature (in kelvins) in the OFF state (i.e., no hot holes) for the device with  $L_{\rm DS} \geq 200$  nm.

extracted from hydrodynamic simulations, where the hole energy  $(E_h)$  is given by the relation

$$E_h = 3kT_h/2\tag{1}$$

where k is the Boltzmann constant and  $T_h$  is the hole temperature. A significant BTBT current in the OFF state is evident from Fig. 2. The surface BTBT current causes hot-hole generation in the OFF state, which causes severe gate oxide reliability issues [3] and eventually leads to early TDDB and permanent failure of the DeMOS device.

Fig. 3 shows that, by increasing the  $L_{\rm DS}$  (Fig. 1) from 0 (standard device layout) to 200 nm or more (proposed device layout), one can mitigate the surface BTBT. This behavior is attributed to the increased tunnelling width (valance band to conduction band, w.r.t. electrons) by shifting the  $N^+$  drain diffusion away from the gate edge. This helps in reducqing the excess leakage current in the OFF state by orders of magnitude and eventually helps in improving the gate oxide reliability. This is evident from the inset in Fig. 3, as the hole temperature (i.e., energy) is relaxed significantly. Recently, we have reported

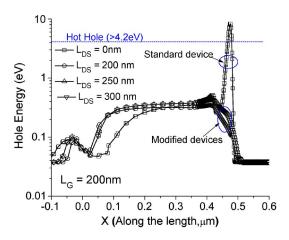

Fig. 4. Simulated (hydrodynamic simulations) hole energy profile along the length of the device, extracted 1 nm below the Si surface, in the OFF state (i.e.,  $V_D=5~\rm V$  and  $V_G=0~\rm V$ ).

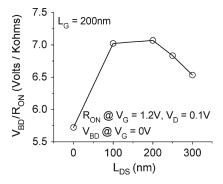

Fig. 5. Simulated  $V_{\rm BD}/R_{\rm ON}$  tradeoff characteristics. It shows an optimum point at  $L_{\rm DS}=200$  nm and 25% improvement in  $V_{\rm BD}/R_{\rm ON}$  tradeoff.  $V_{\rm BD}$  was extracted at  $V_G=0$  and an  $I_D$  compliance of 1  $\mu{\rm A}/\mu{\rm m}$ .

few other ways of reducing BTBT current [1], [2]. However, they lead to degraded  $R_{\rm ON}$  or require an extra masking step.

Furthermore, Fig. 4 compares the hole energy profile (1 nm under the surface) for devices with different  $L_{\rm DS}$ . It shows that increasing the  $L_{\rm DS}$  to 200 nm or more relaxes the carrier (hole for DeNMOS) energy significantly. The proposed modification will greatly help in improving the device reliability. In order to incorporate the proposed modification, a silicide blocking mask is required, in order to block the silicidation in the drain extension region (between gate edge and N<sup>+</sup> drain diffusion), and the proposed modification does not need any other masking or process step. Since the silicide blocking mask already exists in the standard sub-100-nm-node CMOS process, the proposed modification does not require any extra mask or process step.

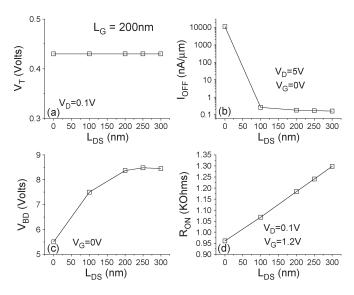

Furthermore, Fig. 5 shows a 25% improvement in the  $V_{\rm BD}/R_{\rm ON}$  tradeoff. It is also evident from the figure that devices give an optimum value of  $V_{\rm BD}/R_{\rm ON}$  tradeoff at  $L_{\rm DS}=200$  nm. For further discussions and comparison of the standard device with the modified device in this brief, we use  $L_{\rm DS}=200$  nm. Fig. 6 shows the change in the device's intrinsic performance (i.e.,  $V_T$ ,  $I_{\rm OFF}$ ,  $V_{\rm BD}$ , and  $R_{\rm ON}$ ) by incorporating the proposed modification. For  $L_{\rm DS}=200$  nm, it shows that, while  $I_{\rm OFF}$  was improved by five orders of magnitude (as discussed earlier),  $R_{\rm ON}$  degrades by less than 20%, which is due to a slight increase in the resistance of extended drain region. Furthermore, it also shows a negligible change in threshold

Fig. 6. Simulated intrinsic characteristics (i.e.,  $V_T$ ,  $I_{\rm OFF}$ ,  $V_{\rm BD}$ , and  $R_{\rm ON}$ ) of the DeMOS device w.r.t.  $L_{\rm DS}$ .

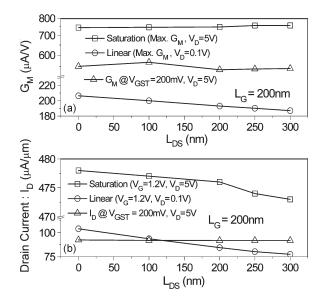

Fig. 7. Simulated impact of gate-to-drain spacing  $(L_{\rm DS})$  over drain current and transconductance  $(G_M)$  under various bias/circuit conditions.

voltage in the linear operating condition of the device and 60% improvement in the breakdown voltage. Improvement in breakdown voltage is explained as follows: Initially, for  $L_{\rm DS}=0$  nm, the device's breakdown was limited due to dominance of surface BTBT, which triggers at lower drain voltages (5.5 V). Whereas, by mitigating the surface BTBT effect, the device's breakdown dominantly depends on impact ionization at Nwell-to-Pwell junction, which occurs at a higher drain voltage. Eventually, this leads to improved  $V_{\rm BD}$  values.

Fig. 7 shows the impact of increasing  $L_{\rm DS}$  over drain current  $(I_D)$  and transconductance  $(G_M)$  of the device under various bias/circuit conditions. It is evident from Fig. 7 that, for  $L_{\rm DS}=200$  nm, there is a negligible degradation in  $I_D$  and  $G_M$  for the following: 1)  $V_{\rm GST}=200$  mV and  $V_D=5$  V and 2) under the device's operation in the saturation region (i.e.,  $V_D=5$  V). On the other hand,  $I_D$  and  $G_M$  degrade by less than 20% and 6%, respectively, for devices' operating in the linear region

(i.e.,  $V_D=0.1~\rm V$ ), due to a slight increase in the resistance of the drift region. It is worth mentioning that the observed degradation in the linear operating condition (under which  $R_{\rm ON}$  versus  $V_{\rm BD}$  is the dominant figure of merit) is in the acceptable range, considering 25% improvement in  $V_{\rm BD}/R_{\rm ON}$  tradeoff.

# IV. CONCLUSION

The standard non-STI-type DeMOS device suffers from the surface BTBT current, which causes early TDDB failure. Increasing  $L_{\rm DS}$  length is the key to improve the surface BTBT current in the device without sacrificing the analog performance of the device for a given value of  $V_{\rm DB}/R_{\rm ON}$  tradeoff. The proposed modification also helps in improving  $V_{\rm DB}/R_{\rm ON}$  tradeoff associated with drain-extended devices for high-voltage applications. Furthermore, it does not lead to any degradation in the digital performance of the device. The proposed modification in the layout does not need any extra mask or process step.

# REFERENCES

- [1] M. Shrivastava, M. S. Baghini, H. Gossner, and V. R. Rao, "I/O device optimization and performance comparison: Part I—Mixed signal performance of various high voltage drain extended MOS devices," *IEEE Trans. Electron Devices*, vol. 57, no. 2, pp. 448–457, Feb. 2010.

- [2] M. Shrivastava, M. S. Baghini, H. Gossner, and V. R. Rao, "I/O device optimization and performance comparison: Part II—A novel scheme to optimize the mixed signal performance and hot carrier reliability of drain extended MOS devices," *IEEE Trans. Electron Devices*, vol. 57, no. 2, pp. 458–465, Feb. 2010.

- [3] D. Varghese, H. Kufluoglu, V. Reddy, H. Shichijo, S. Krishnan, and M. A. Alam, "Universality of off-state degradation in drain extended NMOS transistors," in *IEDM Tech. Dig.*, 2006, pp. 751–754.

- [4] D. Varghese, H. Kufluoglu, V. Reddy, H. Shichijo, D. Mosher, S. Krishnan, and M. A. Alam, "OFF-State degradation in drain-extended NMOS transistors: Interface damage and correlation to dielectric breakdown," *IEEE Trans. Electron Devices*, vol. 54, no. 10, pp. 2669–2678, Oct. 2007.

- [5] G. Hurkx, D. Klaassen, and M. Knuvers, "A new recombination model for device simulation including tunneling," *IEEE Trans. Electron Devices*, vol. 39, no. 2, pp. 331–338, Feb. 1992.

Mayank Shrivastava (S'09–M'10) was born in Lucknow, India, in 1984. He received the B.S. degree in engineering from Rajiv Gandhi Technical University, Bhopal, India, in 2006 and the Ph.D. degree from the Center for Excellence in Nanoelectronics, Department of Electrical Engineering, Indian Institute of Technology (IIT) Bombay, Mumbai, India, in 2010.

From April 2008 to October 2008 and May 2010 to July 2010, he was a Visiting Research Scholar with Infineon Technologies AG, Munich, Germany. Since

September 2010, he has been with Infineon Technologies, East Fishkill, NY, as a Senior Electrostatic Discharge (ESD) Engineer for International Semiconductor Development Alliance. He is the holder of eight patent applications in the fields of ESD, input-output (I/O) devices, FinFETs, and nonvolatile memory. His current research interests include ESD- and hot-carrier-degradation-aware I/O device design, ESD-aware technology development, FinFET and ultrathin-body planar silicon-on-insulator devices, nonvolatile analog memories, and electrothermal modeling and simulation.

Dr. Shrivastava served as a Reviewer for the IEEE TRANSACTIONS ON ELECTRON DEVICES and the 2009 IEEE International Electron Devices Meeting. He was the recipient of Intel's AAF-2008 Best Research Paper Award in circuit design category, IIT Bombay Industrial Impact Award in 2010, an award for his Ph.D. thesis from IIT Bombay named Excellence in Thesis Work in the year 2010, and TR35-2010 Young Innovator Award. His biography was published by the International Biographical Center, Cambridge, U.K., in the 2000 Outstanding Intellectuals of the 21st Century-2010.

**Ruchil Jain** received the B.S. degree from NIT Raipur, India and the M.S. degree from IIT Bombay, Mumbai, India.

Currently, he is with Global Foundry Singapore.

Maryam Shojaei Baghini (M'00–SM'09) received the M.S. and Ph.D. degrees in electrical engineering from Sharif University of Technology, Tehran, Iran, in 1991 and 1999, respectively.

In 1991 and 1992, she was with the Saff and Kavoshgaran Companies, working on the design and test of custom and semicustom ICs. From 1999 to 2000, she was with the Emad Semiconductor Company as a Senior Analog IC Design Engineer. In 2001, she joined the Indian Institute of Technology (IIT) Bombay, Mumbai, India, as a Postdoctoral

Fellow, where she is currently a Faculty Member at the Center for Excellence in Nanoelectronics, Department of Electrical Engineering. She has been the designer/codesigner of several high-performance analog test chips in the industry and academia. She is the author/coauthor of 62 international journals and conference papers and the author of one invited book chapter. She is the holder/coholder of eight patent applications. Her current research interests include device-circuit codesign in emerging technologies, high-performance analog/mixed-signal/RF VLSI design and test, analog/mixed-signal/RF modeling and EDA, power management for system-on-chip applications, high-speed on-chip and off-chip data transmission, analog aspects of digital circuits, and circuit design with organic thin-film components.

Dr. Baghini was a corecipient of the IIT Bombay Industry Impact Award in 2008, the Best Research Award in circuit design at the Intel Corporation AAF 2008, and the third award on research and development at the Fifteenth International Festival of Kharazmi in 2002. Her team of students won the first Cadence Design Systems, Inc., Student Design Contest among SAARC countries in 2006.

**Harald Gossner** (M'06) received the degree in physics (Dipl.Phys.) from the Ludwig-Maximilians University, Munich, Germany, in 1990 and the Ph.D. degree in electrical engineering from the Universität der Bundeswehr, Munich, in 1995.

Since 1995, he has been with Infineon technologies AG, Munich, working on the development of ESD protection concepts for bipolar, BiCMOS, and CMOS technologies. He is the Head of the team of Infineon's center of competence for ESD and external latchup development and also a Senior Principal

who guides the company activities in the field of overvoltage robust design. He has authored and coauthored more than 40 technical papers and one book in the field of ESD.

Dr. Gossner is a member of the management board of the International ESD Workshop (IEW) and a Cochair of the Industry Council on ESD Target Values. He is serving in the TPC of EOS/ESD Symposium, IEDM, and IEW.

V. Ramgopal Rao (M'98–SM'02) received the M.Tech. degree from the Indian Institute of Technology (IIT) Bombay, Mumbai, India, in 1991 and the Dr. Ingenieur degree from the Universitaet der Bundeswehr Munich, Munich, Germany, in 1997.

During 1997–1998 and, again, in 2001, he was a Visiting Scholar with the Department of Electrical Engineering, University of California, Los Angeles. He is currently a Professor with the Center for Excellence in Nanoelectronics, Department of Electrical Engineering, IIT Bombay. He has more than

250 publications in refereed international journals and conference proceedings. He is the holder of three patents, with eight pending patents. His research interests include the physics, technology, and characterization of silicon CMOS devices for logic and mixed-signal application and nanoelectronics.

Prof. Rao is a Fellow of the Indian National Academy of Engineering, the Indian Academy of Sciences, and the Institution of Electronics and Telecommunication Engineers. He is the Editor for the IEEE TRANSACTIONS ON ELECTRON DEVICES in the CMOS devices and technology area and is a Distinguished Lecturer of the IEEE Electron Devices Society. He was the organizing committee Chair for the 17th International Conference on VLSI Design and the 14th International Workshop on the Physics of Semiconductor Devices. He serves on the program/organizing committees of various international conferences, including the International Electron Devices Meeting, IEEE Asian Solid-State Circuits Conference, 2006 IEEE Conference on Nano-Networks, Association for Computing Machinery/IEEE International Symposium on Low Power Electronics and Design, and 11th IEEE VLSI Design and Test Symposium, among others. He was the Chairman of the IEEE AP/ED Bombay Chapter during 2002-2003 and currently serves on the executive committee of the IEEE Bombay Section, besides being the Vice-Chair of the IEEE Asia-Pacific Regions/Chapters Subcommittee. He was the recipient of the Shanti Swarup Bhatnagar Prize in Engineering Sciences in 2005 for his work on electron devices; the Swarnajayanti Fellowship Award for 2003-2004, as instituted by the Department of Science and Technology, Government of India; 2007 IBM Faculty Award; 2008 "The Materials Research Society of India Superconductivity and Materials Science Prize;" and the 2009 TechnoMentor Award instituted by the Indian Semiconductor Association.