# A Novel Drain-Extended FinFET Device for High-Voltage High-Speed Applications

Mayank Shrivastava, Member, IEEE, Harald Gossner, Senior Member, IEEE, and V. Ramgopal Rao, Senior Member, IEEE

Abstract—A novel drain-extended FinFET device is proposed in this letter for high-voltage and high-speed applications. A  $2\times$  better  $R_{\rm ON}$  versus  $V_{\rm BD}$  tradeoff is shown from technology computer-aided design simulations for the proposed device, when compared with a conventional device option. Moreover, a device design and optimization guideline has been provided for the proposed device.

Index Terms—Drain extended, FinFET, high voltage (HV), system-on-a-chip (SoC).

#### I. INTRODUCTION

S THE planar bulk MOS device reaches its scaling limits [1], FinFETs [2] or trigate FETs have become popular in the recent days as the technology option for sub-20-nm gate lengths [3]. Moreover, FinFET-like devices are found to be a suitable option for system-on-a-chip (SoC) application [4], which is indeed reported as the key requirement for reduced cost, size, and power while enjoying a better performance in the technologies below the 20-nm node [5]–[7]. A SoC chip in advance CMOS consists of various functional blocks, which fall into two major voltage classes: 1) low voltage (0.8–1.2 V) and 2) high voltage (HV) (2.5-5 V). In conventional/planar bulk CMOS technology, low-voltage blocks are traditionally implemented by the use of thin gate-oxide and small-channellength devices; however, HV functionalities can be designed by using drain-extended MOS devices [8]. Due to cost-efficient availability of devices in planar CMOS, i.e., lying in various voltage classes, SoC implementation is not an impossible goal. However, the same is not true for FinFET technology, which is due to the challenge to implement HV devices in FinFET technologies.

Keeping HV device requirements for SoC implementation and technological limitations associated with nonplanar process flow in mind, this letter reports a novel drain-extended MOS device for FinFET technology, which we found to be 2× better in terms of on-resistance  $(R_{ON})$  versus junction breakdown voltage  $(V_{\rm BD})$  tradeoff, when compared with a conventional drain-extended FinFET device.

Manuscript received June 7, 2012; revised June 18, 2012; accepted June 24, 2012. Date of publication August 15, 2012; date of current version September 21, 2012. The review of this letter was arranged by Editor W. T. Ng.

M. Shrivastava and H. Gossner are with Intel Mobile Communications Gmbh, 85622 Munich, Germany (e-mail: mayank.shrivastava@intel.com). V. R. Rao is with Indian Institute of Technology Bombay, Mumbai 400 076,

Color versions of one or more of the figures in this letter are available online

at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2012.2206791

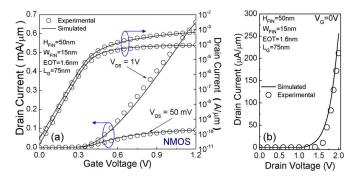

Fig. 1. Calibration of TCAD models for (a) drift-diffusion transport (with quantum corrections) and (b) p-n junction breakdown with experimental data.

#### II. TCAD CALIBRATION AND FRAMEWORK

An undoped trigate FinFET device, which was fabricated with a midgap metal (TiN) gate; a SiON dielectric (effective oxide thickness (EOT) = 1.6 nm); a channel length  $L_G$  of 75 nm; and a target fin width  $W_{\rm FIN}$  of 15 nm were used for TCAD calibration. Fig. 1(a) shows the calibration of TCAD model parameters for drift-diffusion transport considering quantum corrections at the oxide-silicon channel interface, which are carefully matched with the experiments. Moreover, mobility degradation due to thin body/fin was accounted into simulations. Furthermore, we used the New University of Bologna (UniBo2) model for p-n junction breakdown, which was calibrated with experimental data, as shown in Fig. 1(b).

For the investigation of proposed and conventional devices, we further reduced  $W_{\rm FIN}$  and EOT down to 10 and 1 nm, respectively, which were predicted as the target  $W_{\rm FIN}$  and EOT for sub-20-nm-node FinFET technologies [1], [2].

### III. NOVEL DRAIN-EXTENDED FINFET DEVICE

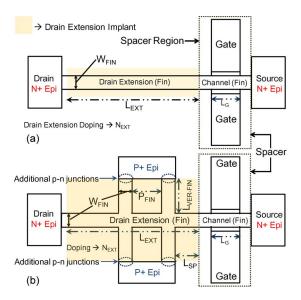

Before we explore a new device concept, it is worth discussing the possible HV device options for FinFET technology by using the conventional understanding of a RESURF LDMOS device for planar fully depleted SOI technology [9], [10]. Fig. 2(a) shows the top view of a conventional HV FinFET SOI device with a lightly doped extended fin region, which allows to increase its breakdown voltage but with the following limitations: 1) Width of the extended drain region is the same as  $W_{\rm FIN}$ , which is not a design parameter for a spacer-defined fin process [11]; 2) increasing  $L_G$  does not help much for  $V_{\rm BD}$ improvement; and 3) the only method to increase  $V_{\rm BD}$  is to reduce extension region doping  $N_{\mathrm{EXT}}$  and increase extension region length  $L_{\rm EXT}$ , which however leads to a severe increase in  $R_{ON}$ .

Fig. 2. Top view of (a) conventional and (b) proposed devices. p+ epitaxy was connected to the same potential as the source, i.e., ground.  $P_{\rm FIN}=40~{\rm nm}$  and  $L_{\rm SP}=40~{\rm nm}$  were used. The additional p-n junctions are formed at p+ epitaxy and longitudinal fin interface.

Fig. 2(b) shows the top view of the proposed drain-extended FinFET (SOI) device, which, in addition to the conventional drain-extended FinFET architecture [see Fig. 2(a)], i.e., a transverse drain-extended region, consists of longitudinal fins (The number of longitudinal fins is represented as  $N_{\rm LONG-FIN}$ .) The longitudinal fins start with a p<sup>+</sup> epitaxial contact (connected to the same potential as the source terminal, i.e., ground or 0 V for nMOS), which then extends into the n<sup>-</sup> region (with length =  $L_{\rm LONG-FIN}$ ) attached with the transverse n<sup>-</sup> region.

Note that the transverse and longitudinal  $n^-$  regions have identical  $n^-$  doping concentration  $N_{\rm EXT}$ , that they form additional p-n junctions, and that longitudinal fins are not along the direction of MOS current. Additional p-n junctions reduce space-charge density for an applied potential at the drain. This is attributed to the extension of the space-charge region along the additional p-n junctions, which eventually relaxes the electric field at the  $n^-$  drain-channel junction. This is already evident from Poisson's equation as follows:

$$\frac{\partial^2 V}{\partial x^2} = -\frac{\partial E}{\partial x} = -\frac{q \cdot \rho}{\epsilon}$$

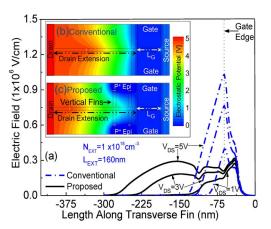

where V is the applied potential, E is the electric field, q is the charge, and  $\rho$  is the space-charge density. Fig. 3(a) shows that the proposed device has a  $3\times$  reduced-peak electric field compared with a conventional device, when 5 V was applied at the drain (gate, source, and body grounded). Additional space-charge regions are formed along the p-n junctions of the longitudinal fin regions. Thus, as shown in the inset in Fig. 3(b) and (c), the proposed device has a significantly relaxed potential distribution near the gate edge, as compared with a conventional device.

## IV. DEVICE DESIGN GUIDELINES AND DISCUSSION

Since longitudinal fins do not influence intrinsic MOS operation, as pointed out in Section III, and the proposed device has a  $3\times$  reduced electric field, one can predict that the proposed device will have a similar  $R_{\rm ON}$  with improved  $V_{\rm BD}$ , as compared

Fig. 3. Physical insight behind the  $V_{\rm BD}/R_{\rm ON}$  performance tradeoff improvement. (a) Comparison of electric field distribution along the transverse fin in conventional and proposed devices. (b)–(c) Two-dimensional electrostatic potential contour across conventional and proposed devices.

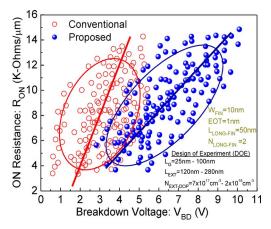

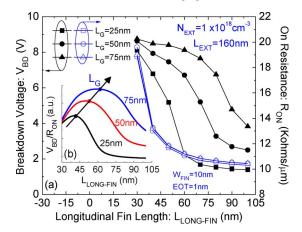

Fig. 4. DOE simulated for conventional and proposed devices.

Fig. 5. Optimization of longitudinal fin length as a function of gate length ( $N_{\rm LONG-FIN}=2$  was used).

with a conventional device. The design-of-experiment results obtained through simulations for conventional and proposed devices in Fig. 4 validate our prediction furthermore and show that the proposed device achieved a  $\sim 2\times$  better  $R_{\rm ON}$  versus  $V_{\rm BD}$  tradeoff.

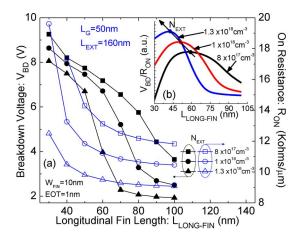

Figs. 5 and 6 derive the optimization criterion for  $L_{\rm LONG-FIN}$  and its relation with  $L_G$  and  $N_{\rm EXT}$ , respectively, while keeping  $L_{\rm EXT}$  fixed. Figs. 5(a) and 6(a) show that  $V_{\rm BD}$  and  $R_{\rm ON}$  increase with different rates when  $L_{\rm LONG-FIN}$  was

Fig. 6. Optimization of longitudinal fin length as a function of drain extension doping ( $N_{\rm LONG-FIN}=2$  was used).

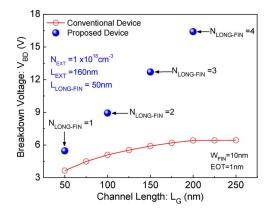

Fig. 7. Impact of channel length on the breakdown voltage of conventional and proposed devices and its relation with the number of longitudinal fins in the proposed device. Note that the symbol representing the proposed device shows only the optimum  $V_{\rm BD}/R_{\rm ON}$  points corresponding to different  $N_{\rm LONG-FIN}.$  Note that the proposed device can achieve significantly higher breakdown voltages without increasing the gate-oxide thickness.

reduced below a certain value depending on the respective  $L_G$  and  $N_{\rm EXT}$  values. In addition to this, Figs. 5(b) and 6(b) show the optimum value of  $L_{\rm LONG-FIN}$ , i.e.,  $V_{\rm BD}$  should be much higher than the  $R_{\rm ON}$  cost adder (maximum  $V_{\rm BD}/R_{\rm ON}$ ), as a function of  $L_G$  and  $N_{\rm EXT}$ . Overall, Figs. 5 and 6 show how the  $V_{\rm BD}/R_{\rm ON}$  tradeoff can be improved by keeping  $L_{\rm LONG-FIN}$  approximately equal to 50 nm. It is worth pointing out that such an optimization is not possible for a conventional device option. Note that  $P_{\rm FIN}$  and  $L_{\rm SP}$  have no impact on  $V_{\rm BD}$ .

So far, the optimization of  $L_{\rm LONG-FIN}$  and its relation with  $L_G$ ,  $L_{\rm EXT}$ , and  $N_{\rm EXT}$  are well understood, and the only unrevealed parameter remaining is the number of longitudinal fins  $N_{\rm LONG-FIN}$ . Fig. 7 shows that  $V_{\rm BD}$  increases with channel length but saturates after a certain value of  $L_G$ , which depends on  $N_{\rm EXT}$  and  $L_{\rm EXT}$ . However, the proposed device behaves differently when  $N_{\rm LONG-FIN}$  and  $L_G$  are increased at the same time. Increasing  $N_{\rm LONG-FIN}$  and  $L_G$  simultaneously leads to a much higher breakdown voltage for fixed  $N_{\rm EXT}$  and  $L_{\rm EXT}$ . This is due to the fact that increasing  $N_{\rm LONG-FIN}$  increases the region of the fin that is affected by the reverse p-n junction area and eventually relaxes the space-charge density (and electric field) for an applied voltage at the drain. Higher  $N_{\rm LONG-FIN}$  for smaller  $L_G$  does not improve  $V_{\rm BD}$  because, for smaller  $L_G$ , channel-to-"drain extension" junction electric field dominates

$V_{\mathrm{BD}}$ . This can be attributed to the insufficient amount of space-charge contribution by longitudinal fins lying far away from the gate edge.

## V. CONCLUSION

Additional longitudinal fins in the proposed drain-extended FinFET device have improved the breakdown voltage of the device without influencing the MOS behavior. Because of this, the proposed drain-extended FinFET device shows a  $2\times$  better  $R_{\rm ON}$  versus  $V_{\rm BD}$  tradeoff. Further optimization of  $V_{\rm BD}$  versus  $R_{\rm ON}$  tradeoff in terms of device design parameters such as  $L_G$  and  $N_{\rm LONG-FIN}$  for a given  $N_{\rm EXT}$  is presented. Such an optimization cannot be achieved for a conventional drain-extended FinFET device. It is worth pointing out that the proposed device can achieve a significantly higher breakdown voltage at a lower gate-oxide thickness, opening up new opportunities for HV high-speed (or RF) applications. The proposed device is also expected to show improved gate-oxide reliability and electrostatic discharge hardness because of the relaxed electric fields and an increased silicon volume.

#### REFERENCES

- [1] International Technology Roadmap for Semiconductors (ITRS), 2009.

- [2] M. Shrivastava, R. Mehta, S. Gupta, N. Agrawal, M. S. Baghini, D. K. Sharma, T. Schulz, K. Arnim, W. Molzer, H. Gossner, and V. R. Rao, "Toward system on chip (SoC) development using FinFET technology: Challenges, solutions, process co-development and optimization guidelines," *IEEE Trans. Electron Devices*, vol. 58, no. 6, pp. 1597– 1607, Jun. 2011.

- [3] Various Publ., Intel Increases Transistor Speed by Building Upward, May 2011.

- [4] C.-C. Yeh, C.-S. Chang, H.-N. Lin, W.-H. Tseng, L.-S. Lai, T.-H. Perng, T.-L. Lee, C.-Y. Chang, L.-G. Yao, C.-C. Chen, T.-M. Kuan, J. J. Xu, C.-C. Ho, T.-C. Chen, S.-S. Lin, H.-J. Tao, M. Cao, C.-H. Chang, T.-C. Ko, N.-K. Chen, S.-C. Chen, C.-P. Lin, H.-C. Lin, C.-Y. Chan, H.-T. Lin, S.-T. Yang, J.-C. Sheu, C.-Y. Fu, S.-T. Hung, F. Yuan, M.-F. Shieh, C.-F. Hu, and C. Wann, "A low operating power FinFET transistor module featuring scaled gate stack and strain engineering for 32/28 nm SoC technology," in IEDM Tech. Dig., 2010, pp. 34.1.1–34.1.4.

- [5] M. Fulde, D. Schmitt-Landsiedel, and G. Knoblinger, "Analog and RF design issues in high-k and multi-gate CMOS technologies," in *IEDM Tech. Dig.*, 2009, p. 1.

- [6] S. Borkar, "Design challenges for 22 nm CMOS and beyond," in *IEDM Tech. Dig.*, 2009, p. 1.

- [7] C. H. Jan, M. Agostinelli, M. Buehler, Z.-P. Chen, S.-J. Choi, G. Curello, H. Deshpande, S. Gannavaram, W. Hafez, U. Jalan, M. Kang, P. Kolar, K. Komeyli, B. Landau, A. Lake, N. Lazo, S.-H. Lee, T. Leo, J. Lin, N. Lindert, S. Ma, L. McGill, C. Meining, A. Paliwal, J. Park, K. Phoa, I. Post, N. Pradhan, M. Prince, A. Rahman, J. Rizk, L. Rockford, G. Sack, A. Schmitz, H. Tashiro, C. Tsai, P. Vandervoorn, J. Xu, L. Yang, J.-Y. Yeh, J. Yip, K. Zhang, Y. Zhang, and P. Bai, "A 32 nm SoC platform technology with 2nd generation high-k/metal gate transistors optimized for ultra low power, high performance, and high density product applications," in IEDM Tech. Dig., 2009, pp. 1–4.

- [8] M. Shrivastava, M. S. Baghini, H. Gossner, and V. R. Rao, "Part I: Mixed-signal performance of various high-voltage drain-extended MOS devices," *IEEE Trans. Electron Devices*, vol. 57, no. 2, pp. 448–457, Feb. 2010.

- [9] S. Sharbati and M. Fathipour, "Investigation of vertical scaling on breakdown voltage and presentation of analytical model for electric field distribution in SOI RESURF LDMOSFET," in *Proc. Int. Semicon. Device Res.* Symp., 2009, pp. 1–2.

- [10] S. Merchant, E. Arnold, H. Baumgart, R. Egloff, T. Letavic, S. Mukherjee, and H. Pein, "Dependence of breakdown voltage on drift length and buried oxide thickness in SOI RESURF LDMOS transistors," in *Proc. Power Semicon. Devices ICs*, 1993, pp. 124–128.

- [11] Y.-K. Choi, T.-J. King, and C. Hu, "A spacer patterning technology for nanoscale CMOS," *IEEE Trans. Electron Devices*, vol. 49, no. 3, pp. 436– 441, Mar. 2002.