# Part II: Design of Well Doping Profile for Improved Breakdown and Mixed-Signal Performance of STI-Type DePMOS Device

Ketankumar H. Tailor, *Student Member, IEEE*, Mayank Shrivastava, *Member, IEEE*, Harald Gossner, *Senior Member, IEEE*, Maryam Shojaei Baghini, *Senior Member, IEEE*, and Valipe Ramgopal Rao, *Senior Member, IEEE*

Abstract—Shallow-trench isolation drain extended pMOS (STI-DePMOS) devices show a distinct two-stage breakdown. The impact of p-well and deep-n-well doping profile on breakdown characteristics is investigated based on TCAD simulations. Design guidelines for p-well and deep-n-well doping profile are developed to shift the onset of the first-stage breakdown to a higher drain voltage and to avoid vertical punch-through leading to early breakdown. An optimal ratio between the OFF-state breakdown voltage and the ON-state resistance could be obtained. Furthermore, the impact of p-well/deep-n-well doping profile on the figure of merits of analog and digital performance is studied. This paper aids in the design of STI drain extended MOSFET devices for widest safe operating area and optimal mixed-signal performance in advanced system-on-chip input-output process technologies.

Index Terms—Avalanche breakdown, drain extended MOSFET (DeMOS), input–output (I/O), mixed-signal performance, OFF-state breakdown voltage, ON-state resistance, two-stage breakdown, well doping profile.

# I. Introduction

RAIN EXTENDED MOSFETs (DeMOSs) and laterally diffused MOS (LDMOS) devices are versatile building blocks in input—output (I/O) interface circuits operating at different power supply voltages, mainly above the core supply level [1]. Due to an asymmetric drain structure, they provide a high breakdown voltage. Both p-type and n-type DeMOS devices can be easily integrated into the standard triple-well CMOS process technology. Since these devices need to handle

Manuscript received December 3, 2014; accepted October 6, 2015. Date of publication October 26, 2015; date of current version November 20, 2015. This work was supported by Intel Mobile Communication GmbH, Munich, Germany. The review of this paper was arranged by Editor M. Darwish. (Corresponding author: Ketankumar H. Tailor.)

K. H. Tailor, M. S. Baghini, and V. R. Rao are with the Centre of Excellence in Nanoelectronics, Department of Electrical Engineering, IIT Bombay, Mumbai 400076, India (e-mail: ketanht@ee.iitb.ac.in; ketanht@gmail.com; mshojaei@ee.iitb.ac.in; rrao@ee.iitb.ac.in).

M. Shrivastava is with the Advance Nanoelectronic Device and Circuit Research Laboratory, Department of Electronic Systems Engineering, Indian Institute of Science, Bangalore 560012, India (e-mail: mayank@dese.iisc.ernet.in).

H. Gossner is with Intel Mobile Communications GmbH, Munich 85579, Germany (e-mail: harald.gossner@intel.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2015.2488683

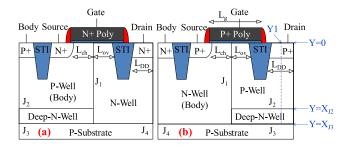

Fig. 1. Schematics of (a) STI-DeNMOS and (b) STI-DePMOS device structures under study. The design of doping concentration profile along the vertical cutline Y1 (through the middle of the drain diffusion region) and the role of junctions  $J_1$ – $J_4$  in improving breakdown performance of STI-DePMOS are described in Section III.

larger operating voltages and currents relative to core logic devices, robustness under high-current and high-voltage operation is essential. A high OFF-state breakdown voltage ( $V_{\rm BD}$ ), a low ON-state resistance ( $R_{\rm ON}$ ), mixed-signal device performance, robustness against electrostatic discharge, and hot-carrier stresses are the main figure of merits of high-voltage devices [1], [2]. Device concepts, such as reduced surface field (RESURF) LDMOS [3] and superjunction LDMOS [4], improve the ON-resistance and OFF-state breakdown voltage. In [5], an n-type RESURF implant under field oxide is used to enhance LDMOS safe operating area (SOA) without degrading the OFF-state breakdown voltage and ON-resistance.

In [6], the physical mechanisms of two-stage drain breakdown characteristics were studied, which were measured on a shallow-trench isolation-type drain extended pMOS (STI-DePMOS) device structure (Fig. 1), as described in Section II. The analyses revealed that the coupling between junctions  $J_1$ ,  $J_2$ , and  $J_3$  [Fig. 1(b)], as the drain voltage is increased, is responsible for triggering of the two stages of breakdown. We showed that the first-stage breakdown occurs due to the vertical punch-through, resulting in poor SOA of the device, whereas the second-stage breakdown occurs due to avalanche breakdown of lateral n-well/p-well junction. This paper is organized as follows. Section II describes the device structures, the output characteristics of STI-DePMOS, and the simulation setup. Then, Section III investigates in depth the design of p-well and deep-n-well doping profile of an

0018-9383 © 2015 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

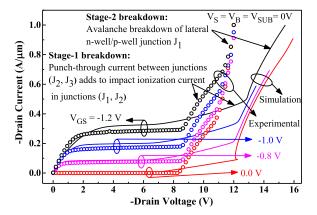

Fig. 2. Drain output characteristics of a (reference) STI-DePMOS device depicting a unique two-stage breakdown behavior. Both experimental and simulated dc characteristics are compared.

STI-DePMOS device. It provides insights into breakdown mechanisms for each profile design and describes how to improve both the OFF-state breakdown voltage and ON-state resistance. Section IV describes the impact of well doping profile on analog, RF, and digital performance figure of merits. Since the same triple-well CMOS process is used for both n- and p-type DeMOS devices, the impact of the optimal well doping for STI-DePMOS on the performance of STI drain extended NMOS (STI-DeNMOS) is studied in Section V. Finally, conclusions are drawn in Section VI.

# II. DEVICE STRUCTURE, *I–V* CHARACTERISTICS, AND SIMULATION SETUP

#### A. Device Structure and I-V Characteristics

Fig. 1 shows the schematics of the STI-DeNMOS and STI-DePMOS devices under study. Each structure uses the three wells: 1) n-well; 2) p-well; 3) and deep-n-well. The deep-n-well of higher resistivity is added below p-well in a triple-well CMOS process to isolate analog and digital circuits in mixed-signal integrated circuits. The mixed-signal performance of STI-DeMOS devices is significantly degraded compared with non-STI-type DeMOS devices due to higher drift region resistance of the STI structure and subsurface carrier current path outside gate control [1]. All the device geometric parameters labeled in Fig. 1(a) and (b) are the same as those defined in [6]. These values are valid for both measured (actual) devices and simulated (reference) devices. As shown in Fig. 2, experimental and simulated  $I_D$ – $V_D$  characteristics of STI-DePMOS exhibit a two-stage breakdown behavior. While the discrepancy in the quantitative values between the simulation and the experiment is due to the details of the doping profile, the qualitative two-stage breakdown behavior is properly reflected by the simulation. First- and second-stage breakdown in the simulated OFF-state drain characteristics are, respectively, triggered at  $V_{DS} = -4.9$  and -12.1 V [6]. The simulated output characteristics in Fig. 2 are used as reference  $I_D$ – $V_D$  characteristics that are to be optimized (in Sections III and IV) for high breakdown voltage and mixedsignal performance. For the simulated reference device, the OFF-state breakdown voltage  $(V_{BD})$ , which is defined as the

TABLE I

MODIFICATIONS OF p-WELL AND DEEP-n-WELL DOPING PROFILES OF STI-DePMOS DEVICES USING PROCESS SIMULATION

| Device | P-Well Parameters                          | Deep-N-Well Parameters                        |

|--------|--------------------------------------------|-----------------------------------------------|

| A      | Dose –, Energy ↓ Peak doping –, Depth ↓    | Dose –, Energy –<br>Peak doping ↑, Depth –    |

| В      | Dose –, Energy ↑<br>Peak doping ↓, Depth ↓ | Dose ↑↑, Energy ↑↑<br>Peak doping ↑↑, Depth ↑ |

| C      | Dose ↓, Energy ↓<br>Peak doping –, Depth ↓ | Dose ↓, Energy –<br>Peak doping –, Depth –    |

| D      | Dose ↑, Energy ↓<br>Peak doping ↑, Depth ↓ | Dose ↑, Energy –<br>Peak doping –, Depth –    |

| E      | Dose ↑, Energy ↑<br>Peak doping ↑, Depth ↑ | Dose ↑↑, Energy ↑↑<br>Peak doping ↑, Depth ↑  |

| F      | Dose ↑, Energy ↑<br>Peak doping ↑, Depth ↑ | Dose ↑↑, Energy ↑<br>Peak doping ↑↑, Depth ↑  |

| G      | Dose ↓, Energy ↑<br>Peak doping ↓, Depth – | Dose –, Energy –<br>Peak doping –, Depth –    |

The symbol  $\uparrow$  means increase,  $\uparrow \uparrow$  greater increase,  $\downarrow$  decrease,  $\downarrow \downarrow$  greater decrease and - means no significant change. The changes of *p*-well and deep-*n*-well parameters in modified devices are relative to reference device.

$V_{\rm DS}$  value at  $V_{\rm GS}=0$  V and  $I_D=-0.1$  nA/ $\mu$ m, is -5.3 V. All process simulations in this paper are performed using [7]. The same device simulation models [8] as used in Part I of this paper [6] are used for dc, ac, and transient device simulations.

#### B. Simulation Setup for Modified Devices

As discussed in [6], the first-stage breakdown voltage of the STI-DePMOS device (punch-through voltage p-well/deep-n-well/p-substrate) is determined by doping profiles of p-well/deep-n-well junction  $J_2$  region, and the second-stage breakdown voltage is the avalanche breakdown voltage of p-well/n-well junction  $J_3$ . Since the breakdown characteristics are affected by p-well and deep-n-well layers [6], doping profiles in these layers are varied using process simulations. The doping profile in n-well (body) is kept unchanged. By varying implantation dose and energy parameters for p-well and deep-n-well in the reference device (described in Table I), devices with modified profiles  $(A, B, C, \ldots, G)$  are obtained. The changes in peak doping concentration in deeper regions of the two wells and the well depths  $y = X_{J2}$  and  $y = X_{J3}$  (at the end of a source/drain diffusion cycle) are also described in Table I. The values of doses and energies are selected so that p-well and deep-n-well have different peak doping and depths in the modified devices. Hence, devices with a wide range of OFF-state breakdown voltages  $(V_{BD})$  could be obtained. Their OFF-state breakdown characteristics and ON-state resistance  $(R_{ON})$  are investigated in detail in Section III. For each device, junction depths of p-well/deep-n-well junction  $J_2$  ( $y = X_{J2}$ ) and deep-n-well/ p-substrate  $J_3$  ( $y = X_{J3}$ ) (with respect to the silicon surface at y = 0) get modified along the vertical cutline Y1 through the

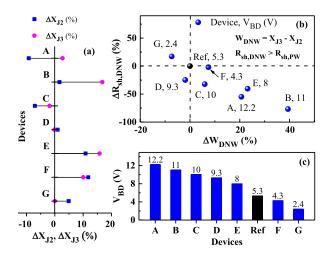

Fig. 3. Percentage change in (a) junction depths  $X_{J2}$  and  $X_{J3}$  and (b) width  $(W_{\rm DNW})$   $(\mu {\rm m})$  and sheet resistance  $(R_{\rm sh,DNW})$   $(\Omega/{\rm sq.})$  of a deepn-well layer for different devices with respect to the reference device. Values of OFF-state breakdown voltage  $V_{\rm BD}$  are also shown in (b). (c)  $V_{\rm BD}$  decreases from device A to G.

middle of the drain diffusion region [Fig. 1(b)]. Also, sheet resistances (1) of p-well ( $R_{\rm sh,PW}$ ) and deep-n-well ( $R_{\rm sh,DNW}$ ) layers are altered. These sheet resistances inversely depend on integrated active dopant concentrations along the vertical cutline Y1 [Fig. 1(b)] through carrier concentrations n and p.  $R_{\rm sh}$  is defined as

$$R_{\rm sh} = \frac{1}{\int_{y_1}^{y_2} q(n\mu_n + p\mu_p) dy}$$

(1)

where  $y_1 = 0$  ( $X_{J2}$ ) and  $y_2 = X_{J2}$  ( $X_{J3}$ ) for  $R_{\rm sh,PW}$  ( $R_{\rm sh,DNW}$ ). In (1), q is the electronic charge, n(p) is the electron (hole) concentration,  $\mu_{\rm n}$  ( $\mu_{\rm p}$ ) is the electron (hole) mobility (both  $\mu_{\rm n}$  and  $\mu_{\rm p}$  are defined using a doping concentration-dependent model [7]), and y is an independent variable along the cutline Y1. For the simulated reference device,  $R_{\rm sh,PW} = 82$   $\Omega/{\rm sq.}$  and  $R_{\rm sh,DNW} = 2694$   $\Omega/{\rm sq.}$

Figs. 3 and 4 describe the variation of  $R_{\rm sh,PW}$  and  $R_{\rm sh,DNW}$  for the modified devices with respect to the reference device. The junction depths  $(X_{J2} \text{ and } X_{J3})$  and the width of deepn-well  $(W_{\rm DNW} = X_{J3} - X_{J2})$  for the modified devices are shown in Fig. 3(a) and (b). The variations in sheet resistances [Figs. 3(b) and 4] are nonmonotonically related to those in junction depths  $(X_{J2}, X_{J3})$ . The dependence of  $V_{\rm BD}$  and  $R_{\rm ON}$  on  $R_{\rm sh,PW}$ ,  $R_{\rm sh,DNW}$ , and  $W_{\rm DNW}$  is discussed in Section III.

#### III. DESIGN OF WELL DOPING PROFILE OF STI-DePMOS

Since  $R_{\rm sh,DNW}$  is significantly larger than  $R_{\rm sh,PW}$ ,  $R_{\rm sh,PW}$  does not affect the OFF-state breakdown voltage  $(V_{\rm BD})$  (the value of  $V_{\rm DS}$  at  $V_{\rm GS}=0$  V and  $I_D=-0.1$  nA/ $\mu$ m). However,  $R_{\rm sh,PW}$  affects the ON-state resistance  $(R_{\rm ON})$  (at  $V_{\rm DS}=-0.1$  V and  $V_{\rm GS}=-1.2$  V), because most of the linear drain current in the p-well region flows closer to the STI under gate-to-drain overlap. As shown in Fig. 3(b), the device  $V_{\rm BD}$  is primarily determined by both  $R_{\rm sh,DNW}$  and the width of the deep-n-well layer  $(W_{\rm DNW}=X_{J3}-X_{J2})$ . The devices are referred to with

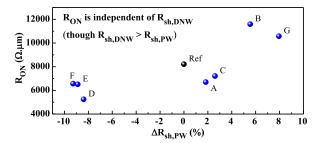

Fig. 4. Variation in ON-state resistance  $R_{\rm ON}$  versus percentage change in the sheet resistance ( $R_{\rm sh,PW}$ ) ( $\Omega/{\rm sq.}$ ) of a p-well layer (with respect to the reference device) for different devices A–G. Devices B and G have higher  $R_{\rm ON}$  compared with other devices due to their relatively higher  $R_{\rm sh,PW}$ .

labels A, B, C, ..., G in decreasing order of their  $V_{\rm BD}$  values [Fig. 3(c)]. The results show that device  $V_{\rm BD}$  can be improved, if  $R_{\rm sh,DNW}$  is decreased by at least 20% (devices A–E).  $W_{\rm DNW}$  is increased for these devices, but slightly reduced for device D. However, the improvement in  $V_{\rm BD}$  reduces at very low  $R_{\rm sh,DNW}$  and very high  $W_{\rm DNW}$  (device B). In addition,  $V_{\rm BD}$  does not improve, if  $W_{\rm DNW}$  is increased without significantly reducing  $R_{\rm sh,DNW}$  (device F). In addition,  $V_{\rm BD}$  significantly degrades at high  $R_{\rm sh,DNW}$  and low  $W_{\rm DNW}$  (device G).

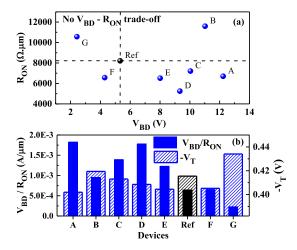

The variations in  $R_{ON}$  with  $R_{Sh,PW}$  in Fig. 4 show that  $R_{\rm ON}$  increases at high  $R_{\rm sh,PW}$ . The values of  $V_{\rm BD}$ ,  $R_{\rm ON}$ ,  $V_{\rm BD}/R_{\rm ON}$  ratio, and  $V_T$  (constant current threshold voltage at  $V_{\rm DS} = -0.1 \text{ V}$  and  $I_D = -0.1 \ \mu\text{A}/\mu\text{m}$ ) for different devices are compared in Fig. 5. Since  $R_{ON}$  is not significantly affected by variations in  $R_{\rm sh,DNW}$  and  $W_{\rm DNW}$ , both  $V_{\rm BD}$  and  $R_{\rm ON}$ for STI-DePMOS can be controlled independently as long as  $R_{\text{sh,PW}}$  is significantly smaller than  $R_{\text{sh,DNW}}$  [Fig. 5(a)] (unlike the conventional LDMOS devices in [4] and [5]). Device A has not only maximum breakdown voltage, but also maximum  $V_{\rm BD}/R_{\rm ON}$  ratio. In addition, device D has minimum ON-state resistance. Since doping in n-well (channel) is kept unchanged, threshold voltages  $V_T$  are relatively unchanged [Fig. 5(b)]. Since at  $V_{DS} = -0.1 \text{ V}$  and  $V_{GS} = -1.2 \text{ V}$ , the current density in the channel region in n-well for different devices is higher than the current density in the p-well drift region, and the variations in  $V_T$  and channel resistance have little contribution to  $R_{ON}$ . In fact,  $R_{ON}$  monotonically varies with  $R_{\rm sh,PW}$  (Fig. 4).

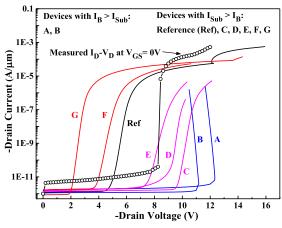

The OFF-state drain breakdown characteristics of the modified devices are compared with the reference device in Fig. 6. Devices A and B show a negative slope in the breakdown region, whereas other devices show a positive slope. For the sake of clarity, the devices in Fig. 6 are distinguished with three different colors, depending on their  $V_{\rm BD}$  values (relative to the reference device) and slope of their breakdown characteristics. It must be noted that the technology-dependent variables  $W_{\rm DNW}$  (= $X_{J3}-X_{J2}$ ),  $R_{\rm sh,PW}$ , and  $R_{\rm sh,DNW}$  are calculated for the vertical profile through the middle of drain diffusion, where the doping concentration gradients are primarily vertical (1-D). Nevertheless, the actual 2-D nature of doping profile at the junctions between p-well, deep-n-well, and n-well (body) (junction lines in Figs. 7–9) also affects  $V_{\rm BD}$  and  $R_{\rm ON}$ , as seen in the deviations in  $V_{\rm BD}$  and  $R_{\rm ON}$

Fig. 5. (a) Comparison of OFF-state breakdown voltage  $V_{\rm BD}$  and ON-state resistance  $R_{\rm ON}$  of different devices A–G, showing no tradeoff between  $V_{\rm BD}$  and  $R_{\rm ON}$ . (b) Comparison of (left)  $V_{\rm BD}/R_{\rm ON}$  ratio and (right) constant current threshold voltage  $V_T$  (at  $V_{\rm DS}=-0.1$  V,  $I_D=-0.1~\mu A/\mu m$ ) of different devices. Device A has both maximum  $V_{\rm BD}/R_{\rm ON}$  ratio. Device D has minimum  $R_{\rm ON}$ .

Fig. 6. Simulated OFF-state breakdown characteristics  $(I_D-V_D)$  at  $V_{\rm GS}=0$  V on log-Y scale) of different devices A–G. Devices A and B (blue lines) show a negative slope in the breakdown region, whereas other devices [devices C, D, and E with high  $V_{\rm BD}$  (magenta lines) and devices F and G with low  $V_{\rm BD}$  (red lines)] show a positive slope. Measured  $I_D-V_D$  at  $V_{\rm GS}=0$  V is also shown for comparison. Legend shows a comparison between n<sup>+</sup>-body  $(I_B)$  and p-substrate  $(I_{\rm Sub})$  currents in the breakdown region for different devices (explained further in Section III).

in Figs. 3(b) and 4. Still, for the initial design, the study based on these variables provides enough physical insights for optimal well doping design to maximize the  $V_{\rm BD}/R_{\rm ON}$  ratio. The detailed physics behind the impact of width and sheet resistance of deep-n-well layer on breakdown characteristics is studied below.

1) Breakdown Physics for Devices A and B: We first investigate breakdown physics for devices A and B, which show distinct negative slope (snapback) in their breakdown characteristics (Fig. 6). For these devices, body current ( $I_B$ ) (at n-well contact) is found to dominate over substrate current ( $I_{Sub}$ ) (at the bottom of p-substrate) in the breakdown region (not shown). The sheet resistance of deep-n-well is reduced, and the width of deep-n-well is increased. This helps in reducing field spreading in the deep-n-well layer when p-well/deep-n-well junction  $I_2$  is under high reverse bias.

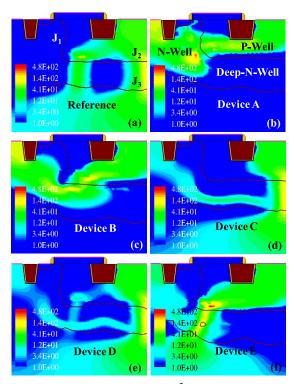

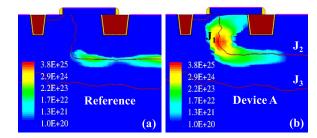

Fig. 7. Conduction current density  $(A/cm^2)$  contour at  $V_{GS} = 0$  V and  $I_D = -0.1 \ \mu A/\mu m$  in different STI-DePMOS devices. (a) Reference. (b) Device A. (c) Device B. (d) Device C. (e) Device D. (f) Device E. Devices in (b)–(f) have higher  $V_{BD}$  compared with the reference device (a).

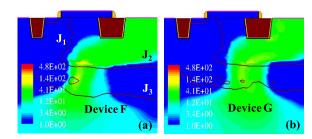

Fig. 8. Conduction current density (A/cm<sup>2</sup>) contour at  $V_{\rm GS}=0$  V and  $I_D=-0.1~\mu{\rm A}/\mu{\rm m}$  in different STI-DePMOS devices. (a) Device F. (b) Device G. Devices in (a) and (b) have lower  $V_{\rm BD}$  compared with the reference device [Fig. 7(a)]. The contour range is kept the same as that of conduction current density in Fig. 7 for the sake of comparison.

Fig. 9. II  $(1/\text{cm}^3)$  contour at  $V_{\text{GS}} = 0$  V and  $I_D = -0.1 \, \mu\text{A}/\mu\text{m}$  in (a) reference device and (b) device A. The II hot spot peaks at junction  $J_2$  for the reference device, whereas it peaks at junction  $J_1$  for device A. However, for all other modified devices B–G, the II hot spot dominates over junction  $J_2$  (not shown).

Figs. 7 and 8 show for different devices the conduction current density contours in the OFF-state at drain current level  $I_D = -0.1 \ \mu \text{A}/\mu \text{m}$  (which is well above the breakdown point

of  $I_D = -0.1 \text{ nA/}\mu\text{m}$ ). Since conduction current density is far lower in the p-substrate region than in the p-well and the deep-n-well for devices A and B, vertical punch-through is avoided, effectively decoupling junctions  $J_2$  and  $J_3$ , unlike the reference device (Fig. 7). In addition, dominant OFF-state current flow is through lateral n-well/p-well junction  $J_1$  for device A [Fig. 7(b)], whereas current flow spreads in the deepn-well through the bottom-left junction between  $J_1$  and  $J_2$  for device B [Fig. 7(c)]. Hence, the reduction in improvement of  $V_{\rm BD}$  for device B compared with device A is because of higher breakdown voltage of lateral junction  $J_1$  (for A) compared with the bottom-left junction region between  $J_1$  and  $J_2$ (for B) (which is determined by relative doping concentration distribution around junctions  $J_1$  and  $J_2$ ). Dominant impact ionization (II) hot spot at  $I_D = -0.1 \, \mu \text{A}/\mu \text{m}$  and  $V_{\text{GS}} = 0 \, \text{V}$ is shifted from vertical p-well/deep-n-well junction  $J_2$ for the reference device to lateral n-well/p-well junction  $J_1$  for device A (Fig. 9). For other devices, peak II occurs at junction  $J_2$  (not shown). Hence, breakdown in device A shows the STI-DeNMOS-like breakdown behavior [6], despite the differences in field distribution due to junction  $J_2$ . Hence, these results indicate that in order to eliminate the two-stage breakdown behavior, the p-well/deep-n-well doping profile should be designed with moderately low sheet resistance (compared with p-well) and moderately high width of deep-n-well layer. This design helps to reduce the peak field around junction  $J_2$ and field spreading in the deep-n-well, thus enhancing the device breakdown voltage and SOA.

2) Breakdown Physics for Devices C-G: Each of the remaining devices C-G exhibit a positive slope in their breakdown characteristics (Fig. 6). In addition, I<sub>Sub</sub> dominates over  $I_B$  in the breakdown region. The breakdown current flow spreads in deep-n-well and p-substrate for each of these devices, indicating the occurrence of punch-through [Figs. 7(d)–(f) and 8]. Their breakdown voltage is determined by drain voltage at the onset of punch-through. It is worth investigating the differences in breakdown voltages for these devices. Devices C-E, which have lower  $R_{sh,DNW}$  (but the reduction in  $R_{sh,DNW}$  is lower compared with devices A and B) and higher  $W_{DNW}$ , have a higher punch-through voltage. Punch-through voltage slightly reduces for device F, because of the 2-D nature of field and current distribution. If  $R_{\text{sh,DNW}}$ is increased and  $W_{DNW}$  is decreased, punch-through voltage drops leading to poor breakdown voltage (device G). Hence, device breakdown voltage can be improved, if punch-through voltage is increased (by reducing  $R_{\rm sh,DNW}$ ).

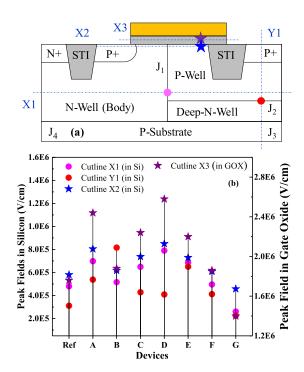

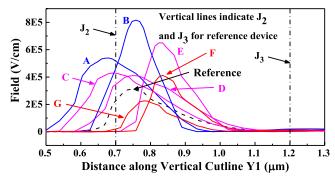

Furthermore, we compare the OFF-state field distribution in STI-DePMOS devices as a function of their well doping profiles (Fig. 10). When devices are biased at  $V_{\rm GS}=0$  V and  $I_D=-0.1~\mu{\rm A}/\mu{\rm m}$ , field distribution has local maxima in different locations. In the silicon region, local peak fields occur along the silicon surface close to the left-side of the STI edge, in the bulk region at lateral junction  $J_1$ , and also in vertical junction  $J_2$ , whereas in gate oxide (GOX), peak field occurs close to the left-side of the STI edge. These peak locations are marked along the cutlines in Fig. 10(a). Fig. 10(b) compares peak fields along four different cutlines in silicon and GOX regions for different devices. The variations in peak field

Fig. 10. (a) Cross section of STI-DePMOS showing locations of 1) vertical cutline Y1 through the middle of the drain diffusion region, 2) lateral cutline X1 at 0.5- $\mu$ m depth below the silicon surface, 3) lateral cutline X2 at 1-nm depth below the silicon surface, and 4) lateral cutline X3 through the middle of GOX. Markers represent peak field spots. (b) Comparison of peak electric fields (V/cm) along different cutlines [shown in (a)] for different STI-DePMOS devices at  $V_{\rm GS}=0$  V and  $I_D=-0.1$   $\mu$ A/ $\mu$ m. Fields across n-well (body)/p-substrate junction  $J_4$  are comparatively negligible.

values are a result of differences in their doping concentration profiles and  $V_{\rm DS}$  at  $V_{\rm GS}=0$  V and  $I_D=-0.1~\mu{\rm A}/\mu{\rm m}$ , which affect their field distributions in different junctions in silicon and GOX. Since peak field in GOX (that occurs close to the left-side of the STI edge) is below 2.6 MV/cm, GOX reliability is not much of an issue. Peak fields that occur along silicon surface (cutline X2) closely follow the variations of peak fields at the lateral junction  $J_1$ .

As shown in Fig. 11, field distribution around junction  $J_2$  along the vertical cutline Y1 for devices B and E have relatively high peak field and less field spreading in their deep-n-well layers compared with other devices, which is determined by their junction depths  $J_2$  and  $J_3$  and doping profiles on either side of junction  $J_2$ . Devices with punchthrough show high field spreading in their deep-n-well.

# IV. IMPACT ON MIXED-SIGNAL PERFORMANCE OF STI-DePMOS DEVICE

In this section, we compare mixed-signal performance of the modified STI-DePMOS devices having higher (improved)  $V_{\rm BD}$  compared with the reference device. Devices A, C, D, and E have lower  $R_{\rm ON}$ , whereas device B has higher  $R_{\rm ON}$  compared with the reference device [Fig. 5(a)].

# A. Analog and RF Performance

The analog and RF device figure of merits and small-signal capacitance-voltage (C-V) characteristics are illustrated

Fig. 11. Electric field (V/cm) distribution along the vertical cutline Y1 [shown in Fig. 10(a)] at  $V_{\rm GS}=0$  V and  $I_D=-0.1~\mu{\rm A}/\mu{\rm m}$  in the reference device and devices A–G. The field at p<sup>+</sup>/p-well interface is much smaller than at junction  $J_2$ . Device A has a relatively low peak field and less field spreading in its deep-n-well layer.

Fig. 12. Left: Peak transconductance  $(G_m)$  at  $V_{\rm DS}=-5$  V, and intrinsic transistor voltage gain  $(G_m/G_{\rm ds})$  (dB) at gate overdrive voltage  $|V_{\rm GS}|-|V_T|=0.1$  V at  $V_{\rm DS}=-5$  V. Right: transconductance per unit drain current  $(G_m/I_D)$  at  $V_{\rm DS}=-5$  V are compared for different devices. The values are normalized with respect to those of the reference device.

Fig. 13. (a)  $C_{\rm GG}-V_D$  and (b)  $C_{\rm GD}-V_D$  plots at  $V_{\rm GS}=-1.2$  V for different devices. (c) Comparison of peak intrinsic cutoff frequency ( $f_T$ ), peak intrinsic maximum oscillation frequency ( $f_{\rm MAX}$ ) (at  $V_{\rm DS}=-5$  V and  $|V_{\rm GS}|>|V_T|$ ) (on the left y-axis), and the product  $V_{\rm BD}\times$  peak- $f_T$  (on the right y-axis) for different devices

in Figs. 12 and 13. As shown in Fig. 12, peak transconductance  $(G_m)$  and transconductance per unit drain current  $(G_m/I_D)$  (transconductance efficiency) at  $V_{\rm DS} = -5$  V are higher for devices with lower  $R_{\rm ON}$  relative to other devices. However, intrinsic transistor voltage gain  $(G_m/G_{\rm ds})$  at  $V_{\rm DS} = -5$  V and  $|V_{\rm GS}| - |V_T| = 0.1$  V

Fig. 14. Comparison of (left) ON-state drain current ( $I_{\rm ON}$ ) (at  $V_{\rm GS}=-1.2~{\rm V}$  and  $V_{\rm DS}=-5~{\rm V}$ ) and (right) OFF-state drain leakage current ( $I_{\rm OFF}$ ) (at  $V_{\rm GS}=0~{\rm V}$  and  $V_{\rm DS}=-5~{\rm V}$ ) for different devices. Device B with maximum  $R_{\rm ON}$  has minimum  $I_{\rm ON}$  and  $I_{\rm OFF}$ .

slightly improves for devices with higher  $R_{\rm ON}$ , because output ac conductance  $G_{\rm ds}$  is less for higher  $R_{\rm ON}$ .

It is worth studying gate capacitance  $(C_{GG})$  and gate-to-drain overlap capacitance  $(C_{GD})$  versus drain voltage curves at  $V_{GS} = -1.2$  V, for different values of p-well doping [Fig. 13(a) and (b)]. The peaking of  $C_{GG}$  and  $C_{GD}$  values at different  $V_{DS}$  values for different devices and the magnitude of the peak values are determined by the spreading of hole charge under gate-to-p-well overlap region in response to the applied small-signal voltage at gate and drain, respectively. Lower p-well doping shifts capacitance peaking to higher drain voltages. The maximum  $C_{\rm GD}$  becomes slightly higher for device D with higher p-well doping. The peak  $C_{GG}$  ( $C_{GD}$ ) increases (decreases) monotonically from device D with minimum  $R_{\rm ON}$  to device B with maximum  $R_{\rm ON}$ . To compare RF performance, both intrinsic cutoff frequency  $(f_T)$ (frequency at unity current gain point) and maximum oscillation frequency ( $f_{MAX}$ ) (frequency at which Mason's unilateral power gain is unity) are extracted from small-signal ac device simulations [8] of STI-DePMOS devices for a fixed  $V_{DS}$  bias of  $V_{DS} = -5$  V and a variable  $V_{GS}$  bias with  $|V_{GS}| > |V_T|$ . Each device shows a peak in  $f_T$  and  $f_{MAX}$  for  $|V_{GS}| > |V_T|$ , and these peak values are compared in Fig. 13(c). Difference in the relative ratio of peak  $f_T$  and  $f_{MAX}$  for different devices is due to differences in their  $G_m$ ,  $C_{GG}$ , and  $C_{GD}$  characteristics in the saturation region. Both peak  $f_T$  and  $f_{MAX}$  degrade for device B with higher  $R_{ON}$  because of its reduced peak  $G_m$ and higher  $C_{GG}$  relative to the reference device. Highest peak  $f_T$  and  $f_{MAX}$  occur for device D with minimum  $R_{ON}$  because of its maximum  $G_m$  and lowest  $C_{GG}$ . In addition, Fig. 13(c) shows that device A with maximum  $V_{\rm BD}/R_{\rm ON}$  has the highest figure of merit for mixed-signal performance parameter of  $V_{\rm BD} \times {\rm peak} f_T$ .

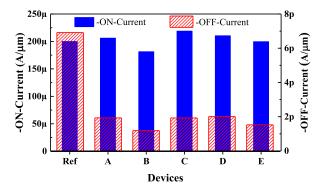

# B. Digital Performance

In addition to analog and RF applications, DeMOS devices are used as high-voltage switches in I/O buffers, voltage level shifters, dc-to-dc converters, and other mixed-signal circuits. Figs. 14–16 compare the digital performance of different STI-DePMOS devices.

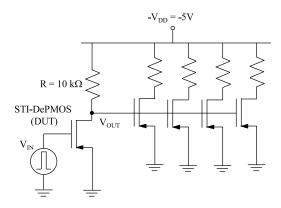

Fig. 15. Schematic of a fanout-of-4 (FO4) inverter used to compute FO4 delay. Source, body, and substrate terminals are grounded.

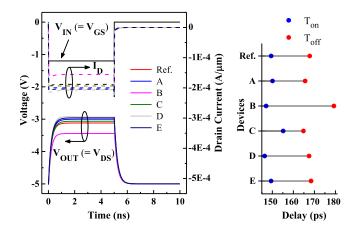

Fig. 16. Left: input gate voltage  $V_{\rm IN}$  (= $V_{\rm GS}$ ), output drain voltage  $V_{\rm OUT}$  (= $V_{\rm DS}$ ) (left y-axis), and output drain current ( $I_D$ ) (right y-axis) waveforms of different devices under fanout-of-4 inverter test circuit. Right: comparison of turn-ON and turn-OFF propagation (FO4) delays ( $T_{\rm ON}$  and  $T_{\rm OFF}$ ) of FO4 inverter with different devices.

Fig. 14 shows a slightly improved OFF-state leakage current ( $I_{OFF}$ ) at  $V_{GS} = 0$  V and  $V_{DS} = -5$  V for the modified devices A–E, which is due to their higher  $V_{\rm BD}$ . In addition, the ON-state drive current  $(I_{ON})$  at  $V_{GS} = -1.2$  V and  $V_{\rm DS} = -5$  V, and  $I_{\rm OFF}$  are minimum for device B with maximum  $R_{ON}$ . To compare the switching (transient) performance of the devices with different doping profiles, they are biased in a fanout-of-4 inverter test circuit with  $R = 10 \text{ k}\Omega$  (Fig. 15). A square pulse of 10-ns width, 10-ps rise/fall time, and -1.2 V amplitude is applied to the gate of the device-under-test (DUT). Output drain voltage  $(V_{DS})$  and drain current  $(I_D)$  waveforms of the DUT are shown in Fig. 16. Turn-ON and turn-OFF propagation delays  $(T_{\rm ON}, T_{\rm OFF})$  are calculated as differences between 50% time points in gate and drain voltage transitions during turn-ON and turn-OFF events, respectively. The different values of  $T_{

m ON}$ and  $T_{\text{OFF}}$  for different devices (Fig. 16) occur due to their different  $I_{ON}$  values (Fig. 14) and capacitance characteristics (Fig. 13), which reflect the alterations in the p-well doping concentration profiles. As shown in Fig. 16, the turn-ON delay  $(T_{ON})$  (which depends on the formation of inversion channel in n-well) is relatively low for devices B and D, despite their differences in  $R_{\rm ON}$ . This is because of lower  $I_{\rm DSAT}$ and  $V_{\rm DSAT}$  and slower charging rate for device B compared

TABLE II

SUMMARY OF DIFFERENT WELL DOPING PROFILES AND IMPACT

ON PERFORMANCE OF STI-DePMOS DEVICES

| Device | P-Well                          | Deep-N-Well                                                                    | Device                                                                             |

|--------|---------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|        | Conditions                      | Conditions                                                                     | Performance                                                                        |

| A      | $R_{ m sh,PW}$ -                | $W_{\mathrm{DNW}} \uparrow, R_{\mathrm{sh,DNW}} \downarrow$                    | $V_{\rm BD} \uparrow, R_{\rm ON} \downarrow$                                       |

| C      | $R_{ m sh,PW}$ -                | $W_{\mathrm{DNW}} \uparrow, R_{\mathrm{sh,DNW}} \downarrow$                    | Analog/digital                                                                     |

| D      | $R_{ m sh,PW} \downarrow$       | $W_{\mathrm{DNW}}\downarrow$ , $R_{\mathrm{sh,DNW}}\downarrow$                 | FOM improve                                                                        |

| E      | $R_{\mathrm{sh,PW}} \downarrow$ | $W_{\mathrm{DNW}} \uparrow, R_{\mathrm{sh,DNW}} \downarrow$                    |                                                                                    |

| В      | $R_{ m sh,PW}$ $\uparrow$       | $W_{\mathrm{DNW}}\uparrow\uparrow$ , $R_{\mathrm{sh,DNW}}\downarrow\downarrow$ | $V_{\rm BD}$ $\uparrow$ , $R_{\rm ON}$ $\uparrow$<br>Analog/digital<br>FOM degrade |

| F      | $R_{ m sh,PW} \downarrow$       | $W_{\mathrm{DNW}} \uparrow$ , $R_{\mathrm{sh,DNW}}$ -                          | $V_{\mathrm{BD}}\downarrow$ , $R_{\mathrm{ON}}\downarrow$                          |

| G      | $R_{ m sh,PW}$ $\uparrow$       | $W_{\mathrm{DNW}}\downarrow,R_{\mathrm{sh,DNW}}\uparrow$                       | $V_{\mathrm{BD}}\downarrow$ , $R_{\mathrm{ON}}\uparrow$                            |

The width  $W_{\rm DNW}$  of deep-n-well layer is difference between junction depths  $X_{13}$  and  $X_{12}$  (shown in Fig. 3(a)). The symbol  $\uparrow$  means increase,  $\uparrow \uparrow$  greater increase,  $\downarrow \downarrow$  decrease,  $\downarrow \downarrow \downarrow$  greater decrease and - means no significant change. Analog and digital performance figure-of-merits (FOM) are compared for devices A-E with higher breakdown voltage, and not for devices F-G.

TABLE III

PERCENTAGE CHANGES IN FIGURE OF MERITS OF MODIFIED

STI-DeNMOS DEVICES COMPARED WITH THE

REFERENCE DEVICE

| Figure-of-merit                                                                       | Percentage change (%) for type A | Percentage change (%) for type D |

|---------------------------------------------------------------------------------------|----------------------------------|----------------------------------|

| $V_{\rm BD}$ ( $V_{\rm DS}$ at $V_{\rm GS} = 0$ V,<br>$I_{\rm D} = 0.1$ nA/ $\mu$ m)  | -4 ↓                             | -10.6 ↓                          |

| $R_{\rm ON}$ (at $V_{\rm DS} = 0.1 \text{ V}$ )                                       | +5.5 ↑                           | 13.6 ↑                           |

| $V_{ m BD}/R_{ m ON}$                                                                 | -9 ↓                             | -21.3 ↓                          |

| $V_{\rm T}$ (at $V_{\rm DS} = 0.1 \text{ V}$ )                                        | -0.1 ↓                           | -0.9 ↓                           |

| Peak $G_{\rm m}$ (at $V_{\rm DS} = 5 \text{ V}$ )                                     | -2.8 ↓                           | -6.1 ↓                           |

| $G_{\rm m}/I_{\rm D}$ (at $V_{\rm DS}$ = 5 V<br>and $V_{\rm GS}-V_{\rm T}$ = 0.1 V)   | +1.3 ↑                           | -3.1 ↓                           |

| $G_{\rm m}/G_{\rm DS}$ (dB) (at $V_{\rm DS}$ = 5 V, $V_{\rm GS} - V_{\rm T}$ = 0.1 V) | +6.4 ↑                           | 11.9 ↑                           |

| Peak $f_{\rm T}$ (at $V_{\rm DS} = 5 \text{ V}$ )                                     | -6.5 ↓                           | -10.1 ↓                          |

| Peak $f_{\text{MAX}}$ (at $V_{\text{DS}}$ =5V)                                        | -27 ↓                            | -10 ↓                            |

| $I_{\rm ON}$ (at $V_{\rm DS} = 5$ V)                                                  | -6 ↓                             | -10.3 ↓                          |

| $I_{\rm OFF}$ (at $V_{\rm DS} = 5 \text{ V}$ )                                        | -6.5 ↓                           | -15.9 ↓                          |

| Turn-on-delay $(T_{on})$                                                              | +2.2 ↑                           | +1.92 ↑                          |

| Turn-off-delay ( $T_{\text{off}}$ )                                                   | +0.34 ↑                          | -1.35 ↓                          |

Reference STI-DeNMOS is simulated with the reference process flow, whereas modified STI-DeNMOS devices with doping profile of types *A* and *D* as used for *p*-well and deep-*n*-well in STI-DePMOS devices (in Section III). For delay calculations, same FO4 inverter test circuit (Fig. 15) with voltages of inverted polarity is used (source, body and substrate terminals are grounded).

with device D. The turn-OFF delay ( $T_{\rm OFF}$ ) (which depends on removal of hole charge from channel and drift regions) is relatively high for device B because of its low  $I_{\rm ON}$  and high  $C_{\rm GG,peak}$ .

Table II highlights the variation of sheet resistance of p-well ( $R_{\rm sh,PW}$ ) and deep-n-well ( $R_{\rm sh,DNW}$ ) and the width of deep-n-well ( $W_{\rm DNW}$ ) for the devices investigated in this paper (Section III). Table II also shows the impact of these variations on the device performance with respect to the reference device.

#### V. IMPACT ON PERFORMANCE OF STI-DeNMOS DEVICE

In Section III, it was shown that the STI-DePMOS devices A and D have the highest  $V_{\rm BD}/R_{\rm ON}$  ratio and minimum  $R_{\rm ON}$ , respectively, compared with other devices (Fig. 5). Since the same process steps are also used for p-well (body) and deep-n-well in STI-DeNMOS in a triple-well CMOS technology [Fig. 1(a)], we investigate the impact of using the well doping profile of STI-DePMOS devices A and D on breakdown and mixed-signal performance of STI-DeNMOS, keeping the doping profile in n-well (drift region of STI-DeNMOS) unchanged. Table III shows that  $V_{\rm BD}$ ,  $R_{\rm ON}$ ,  $V_{\rm BD}/R_{\rm ON}$  ratio,  $I_{\rm ON}$ , peak  $G_m$ ,  $G_m/I_D$ , peak  $f_T$  and  $f_{MAX}$ , and propagation delays slightly degrade, whereas  $I_{OFF}$  and  $G_m/G_{ds}$  improve for the modified devices. The percentage changes in the performance parameters are results of variation in 2-D doping profiles at n-well/p-well junction  $J_1$  in the modified STI-DeNMOS devices that affects the distributions of fields, current density, and carrier density in OFF- and ON-states. Though the best doping profiles (among the profiles investigated in Section III) for STI-DePMOS device affect the performance of STI-DeNMOS devices, the improvement in the performance and SOA of STI-DePMOS device (type A) far outweighs the marginal degradation in the performance of the modified STI-DeNMOS devices.

#### VI. CONCLUSION

We have found different ways to tune the OFF-state breakdown voltage and ON-state resistance in STI-DePMOS devices that are implemented in the triple-well CMOS process technology. By increasing the average doping concentration (by enough amount) in the deep-n-well layer, we could avoid the punch-through-induced vertical breakdown, thereby removing the two-stage breakdown behavior. In addition, by slightly increasing the average doping concentration in the deep-n-well layer, we could shift the onset of the first-stage breakdown to a higher drain voltage, thereby offering higher breakdown voltage than the reference device (Section II). Based on the detailed TCAD analyses, we concluded that the best device with the maximum  $V_{\rm BD}/R_{\rm ON}$  ratio can be designed by moderately increasing the width and average doping concentration of the deep-n-well layer. This design generates a peak II hot spot at the lateral n-well/p-well junction, as for the conventional avalanche breakdown in STI-DeNMOS, and hence, it achieves a wider SOA for high-voltage operation. For high-voltage, high-speed, mixed-signal circuits, such as voltage level shifters, dc-to-dc converters, and envelope tracking power amplifiers using I/O devices, mixed-signal performance must also be optimized. Mixed-signal device performance could be improved for devices with relatively higher average doping concentration in the p-well, which have lower ON-state resistance and parasitic capacitances. In order to allow both n- and p-type STI-DeMOS devices made using the triplewell CMOS technology to enjoy maximum SOA and offer high mixed-signal performance, TCAD-based process technology optimization must be performed. The work in this paper gives valuable insights into ways to achieve these goals.

#### ACKNOWLEDGMENT

The authors would like to thank Prof. D. K. Sharma and Prof. A. N. Chandorkar from the Department of Electrical Engineering, IIT Bombay, Mumbai, India, for their useful technical discussions.

#### REFERENCES

- M. Shrivastava, M. S. Baghini, H. Gossner, and V. R. Rao, "Part I: Mixed-signal performance of various high-voltage drain-extended MOS devices," *IEEE Trans. Electron Devices*, vol. 57, no. 2, pp. 448–457, Feb. 2010.

- [2] P. Moens and G. Van den Bosch, "Characterization of total safe operating area of lateral DMOS transistors," *IEEE Trans. Device Mater. Rel.*, vol. 6, no. 3, pp. 349–357, Sep. 2006.

- [3] A. W. Ludikhuize, "A review of RESURF technology," in Proc. 12th Int. Symp. Power Semicond. Devices ICs, 2000, pp. 11–18.

- [4] T. Fujihira, "Theory of semiconductor superjunction devices," Jpn. J. Appl. Phys., vol. 36, no. 10, pp. 6254–6262, Oct. 1997.

- [5] P. Hower, J. Lin, S. Merchant, and S. Paiva, "Using adaptive RESURF to improve the SOA of LDMOS transistors," in *Proc. 12th Int. Symp. Power Semicond. Devices ICs*, 2000, pp. 345–348.

- [6] K. H. Tailor, M. Shrivastava, H. Gossner, M. S. Baghini, and V. R. Rao, "Part I: Physical insights into the two-stage breakdown characteristics of STI-type drain-extended pMOS device," *IEEE Trans. Electron Devices*, vol. 62, no. 12, pp. 4097–4104, Dec. 2015.

- [7] Sentaurus Process User Guide, Version H-2013.03, Synopsys, Inc., Mountain View, CA, USA, 2013.

- [8] Sentaurus Device User Guide, Version H-2013.03, Synopsys, Inc., Mountain View, CA, USA, 2013.

**Ketankumar H. Tailor** (S'15) received the B.Tech. degree in electronics and communication engineering from NIT Surat, Surat, India, in 2008. He is currently pursuing the M.Tech. and Ph.D. degrees in advanced CMOS I/O device technology with IIT Bombay, Mumbai, India.

His current research interests include analysis and design for I/O device reliability, I/O circuit design with electrostatic discharge protection, and the physics and design of nanoscale HV devices.

Mayank Shrivastava (S'09–M'10) received the Ph.D. degree from IIT Bombay, Mumbai, India, in 2010.

He is currently an Assistant Professor with the Indian Institute of Science, Bangalore, India. He has over 45 publications in international journals/conferences and has 25 patents issued or pending in his field of interest. His current research interests include advanced and beyond CMOS, on-chip electrostatic discharging protection, and power devices.

Harald Gossner (M'06–SM'11) received the B.S. (Dipl.Phys.) degree in physics from Ludwig-Maximilians-Universität München, Munich, Germany, in 1990, and the Ph.D. degree in electrical engineering from Universität der Bundeswehr München, Munich, in 1995.

He is currently a Senior Principal Engineer with Intel Mobile Communications GmbH, Munich, where he is involved in the development of robust mobile systems.

Maryam Shojaei Baghini (M'00–SM'09) received the M.S. and Ph.D. degrees in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 1991 and 1999, respectively.

She joined the Department of Electrical Engineering, IIT Bombay, Mumbai, India, in 2001, as a Post-Doctoral Fellow, where she is currently a Professor. Her current research interests include device-circuit co-design in emerging technologies and analog/mixed-signal/RF IC design.

Valipe Ramgopal Rao (M'98–SM'02) received the M.Tech. degree from IIT Bombay, Mumbai, India, in 1991, and the Dr.Ing. degree from Universität der Bundeswehr München, Munich, Germany, in 1997.

He is currently a P. K. Kelkar Chair Professor of the Department of Electrical Engineering and the Chief Investigator with IIT Bombay. He has authored over 380 papers and holds over 30 patents and patent applications.