# Physical Insights Into the Impact of Surface Traps on Breakdown Characteristics of AIGaN/GaN HEMTs—Part I

Vipin Joshi<sup>®</sup>, Sayak Dutta Gupta, *Student Member, IEEE*, Rajarshi Roy Chaudhuri, and Mayank Shrivastava<sup>®</sup>, *Senior Member, IEEE*

Abstract—Impact of surface traps on the breakdown characteristics of AIGaN/GaN HEMT devices is revealed using detailed TCAD computations and supporting experiments. Detailed mechanism explaining the role of surface traps in modulating channel electric field under various surface trap, device design, gate-stack, and applied voltage conditions is discussed. Experimental analysis with different surface conditions shows the measured electric field profile, using electro-luminescence experiments, to be in complete agreement with the computational findings. Device design guidelines with respect to design parameters affecting drift region's electric field and gate-stack in presence of surface traps or varying surface trap concentration is presented.

Index Terms— AIGaN/GaN HEMTs, device breakdown, electric field engineering, surface traps.

## I. INTRODUCTION

RESENCE of traps in AlGaN/GaN HEMTs has proved to be one of the major bottlenecks in device design for power as well as RF applications. Traps on device surface as well as in GaN buffer are the root cause of several reliability phenomena observed in AlGaN/GaN HEMTs [1]–[10]. Besides, due to its ability to modulate surface potential and 2-D electron gas (2DEG) density [11], surface traps are considered as one of the major factors affecting device performance [8], [12]. Considering the impact of surface traps on 2DEG channel, several surface passivation schemes, using nitrogen [13], SiON [14], highly resistive GaN cap layer [15], NiO $_X$ /SiN $_X$  [16], and Al $_2$ O $_3$ /SiN $_X$  [16], have been proposed for improving breakdown voltage ( $V_{\rm BD}$ ) of AlGaN/GaN HEMTs. Although these works demonstrate improvement in  $V_{\rm BD}$  of the device, attempts to explore the physical mechanism

Manuscript received September 28, 2020; accepted October 26, 2020. Date of publication November 18, 2020; date of current version December 24, 2020. This work was supported by the Department of Science and Technology, Indian Institute of Science, Bangalore, Government of India, through the Technology Systems Development Programme's (TSDP) under Project DST/TSG/AMT/2015/294. The review of this article was arranged by Editor G. Meneghesso. (Corresponding author: Vipin Joshi.)

The authors are with the Department of Electronic Systems Engineering, Indian Institute of Science, Bengaluru 560012, India (e-mail: vipinjoshi@iisc.ac.in; mayank@iisc.ac.in).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2020.3034561.

Digital Object Identifier 10.1109/TED.2020.3034561

governing the same has been limited. For example, while surface passivation is expected to passivate surface traps, leaky dielectric experiment by Koudymov  $et\ al.$  [17] suggested that the surface passivation techniques do not passivate the surface traps. Rather, it modulates the interaction of gate contact with surface traps. Similarly, improved RF performance of the device by NH<sub>3</sub> plasma treatment before surface passivation [9] supports the argument that surface traps are present even after surface passivation. Saito  $et\ al.$  [18] reported impact of surface defect charge on gate leakage induced device breakdown, however, impact of surface defect charge on channel electric field was not considered. Similarly, Hanawa  $et\ al.$  [19] discussed the impact of high- $\kappa$  passivating layer on  $V_{\rm BD}$  of AlGaN/GaN HEMTs, however, the authors neglected surface defect charge and did not take into account gate tunneling and leakage.

Bearing these points in mind, it can be concluded that by and large interplay of surface traps, its ionization, and electric field distribution across the HEMT device and its impact on  $V_{\rm BD}$  has not been explored in detail and therefore, is not well understood yet. This work attempts to bridge this gap and discusses the impact of surface traps on the electrical breakdown of AlGaN/GaN HEMTs. To address this, a well calibrated computational setup is used to determine leakage as well as avalanche induced impact ionization generation, thereby allowing accurate prediction of device breakdown. Computational analysis have proved to be vital in exploring physical mechanisms behind such unique phenomena in GaN-based devices [20]-[24]. Through computational analysis, traps on device surface are found to modulate the channel depletion and channel electric field thereby affecting  $V_{\rm BD}$ . Experimentally extracted electric field profile, using electro-luminescence (EL) experiments, on devices with different surface conditions was found to be in complete agreement with the computational findings. Furthermore, impact of surface traps on the device design for achieving high V<sub>BD</sub> in AlGaN/GaN HEMTs is discussed along with the physical insights and mechanism responsible for improvements. In part II of this work, the observed impact of surface traps on channel electric field and  $V_{\rm BD}$  is extended to account for the traps present in GaN buffer. A complex interplay of surface and buffer region traps and its collective role in modulating channel electric field in AlGaN/GaN HEMTs is disclosed in part II.

0018-9383 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

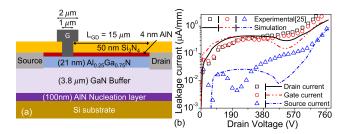

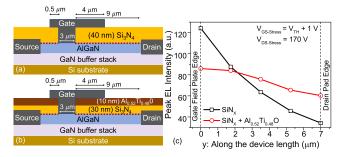

Fig. 1. (a) Device schematic used for computational and experimental studies. (b) Comparison of experimental characteristics [25] with the computed device characteristics depicting an excellent agreement between the two. Substrate terminal was grounded for all the calculations and  $V_{\rm GS} = V_{\rm TH} - 2\,V$  was used to ensure OFF-state operation.

This part of the work is arranged as follows: Section II explains the computational setup used in this work. Section III discusses impact of traps present on the HEMT surface on the  $V_{\rm BD}$  and associated physical mechanism with experimental validation. Section IV discusses device design for achieving high  $V_{\rm BD}$  in AlGaN/GaN HEMTs in presence of surface traps. Finally, Section V concludes the work.

#### II. DEVICE STRUCTURE AND SIMULATION SETUP

Fig. 1(a) depicts schematic of the AlGaN/GaN HEMT architecture [25] used in this work. A well calibrated TCAD setup, adapted from [24], [26], [27], was used to obtain an agreement with the experimental data as depicted in Fig. 1(b). The figure shows an agreement between simulated and experimental data in terms of  $V_{\rm BD}$  as well as leakage current. These computations were done with a fixed acceptor trap concentration of  $\sim 8 \times 10^{16}$  cm<sup>-3</sup> in the GaN buffer to emulate a semiinsulating buffer. On the other hand, donor-type traps on device surface with an activation energy of  $E_C - 0.68$  eV (associated with traps on AlGaN surface [28]) were used to calibrate channel charge density and gate leakage [27].

The simulations considered drift diffusion transport along with high field induced mobility degradation. Quantum correction, lattice, and carrier heating were found to have negligible impact on breakdown calculations and hence were neglected for  $V_{\rm BD}$  calculations. Although gate contact was modeled as Schottky contact, drain, and source contacts were also modeled as Schottky contacts, however, with doping near the S/D-contact/GaN interface and a lower work-function to emulate the ohmic contact formation in GaN HEMTs. This contact profile results in excellent reproduction of experimental conditions [27]. Impact ionization induced carrier generation was taken into account according to Chynoweth law with electron and hole ionization parameters adapted for GaN as described in [29] and [30]. As discussed in our earlier work [24], the adopted model showed good agreement in terms of leakage and breakdown characteristics with experimental data for devices fabricated on a C-doped GaN buffer with different  $L_{GD}$ values. A detailed description of the computational framework can be found in our earlier works [24], [27]. OFF-state  $V_{\rm BD}$  of the device was evaluated at a gate to source voltage  $(V_{GS})$  of  $V_{\rm TH} - 2~{\rm V}~{\rm and~a~drain~current~of~1}~\mu{\rm A/mm}$  [25] with substrate grounded. Here  $V_{\rm TH}$  is threshold voltage of the device.

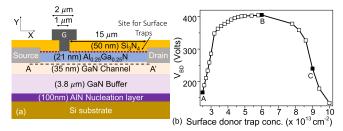

Fig. 2. (a) Simplified device structure depicting site considered for surface traps. AA' depicts the cutline along which lateral electric field is extracted. (b)  $V_{\rm BD}$  as a function of surface donor trap concentration.

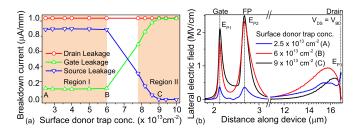

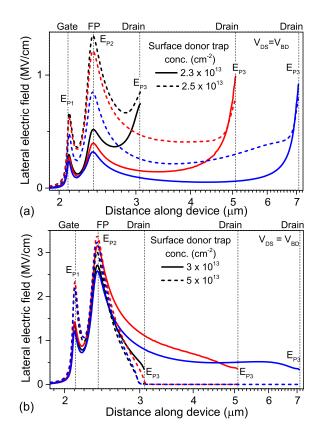

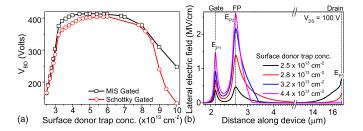

Fig. 3. (a) Different leakage current components extracted at the onset of breakdown for devices with varying surface donor trap concentration. (b) Impact of surface donor trap concentration on lateral channel electric field extracted along cutline AA' [shown in Fig. 2(a)]. Three significant electrical peaks labeled  $E_{P1}$ ,  $E_{P2}$ , and  $E_{P3}$  can be observed.

# III. IMPACT OF SURFACE TRAPS ON ELECTRIC FIELD MODULATION AND BREAKDOWN

Donor-type traps on device surface are a well-known source of 2DEG channel in AlGaN/GaN HEMTs [11], [27]. This section takes into account the influence of surface traps on channel electric field and leakage current to evaluate its impact on  $V_{\rm BD}$ . The device structure used in this section along with the site for surface traps is depicted in Fig. 2(a). Furthermore, the device dimensions, as depicted in Fig. 2(a), are considered throughout this section unless stated otherwise.

### A. Impact of Surface Traps on V<sub>BD</sub>

Impact of surface trap concentration on  $V_{\rm BD}$  of the device is depicted in Fig. 2(b). The figure shows a bell-shaped curve wherein  $V_{\rm BD}$  initially increases with surface trap concentration, reaches a plateau where it remains unchanged, and then reduces when surface trap concentration was increased further. In order to probe the breakdown phenomena, leakage current was measured at all the terminals at the onset of breakdown. Fig. 3(a) compares the drain current with source and gate current at the onset of breakdown for different surface donor trap concentrations. It shows that for lower trap concentrations [Region I in Fig. 3(a)], drain current at the onset of breakdown is governed by source leakage. However, as surface donor trap concentration is increased [Region II in Fig. 3(a)], the drain current is dominated by gate leakage. A comparison of points A, B, and C in Figs. 2(b) and 3(a) show that  $V_{\rm BD}$  improves with the surface donor trap concentration (point  $A \rightarrow B$ ) when source leakage is the major component of drain current (Region I). On the other hand,  $V_{\rm BD}$  reduces

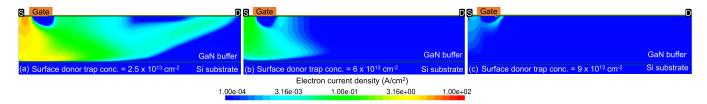

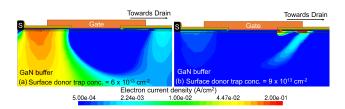

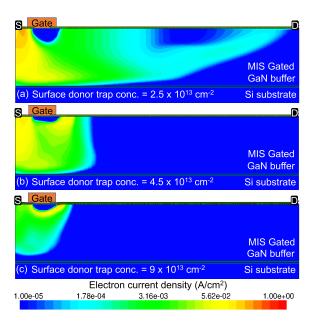

Fig. 4. Comparison of electron current density contours at the onset of electrical breakdown for devices with surface donor trap concentration of (a)  $2.5 \times 10^{13}$  cm<sup>-2</sup>, (b)  $6 \times 10^{13}$  cm<sup>-2</sup>, and (c)  $9 \times 10^{13}$  cm<sup>-2</sup>. A shift in leakage path from drain–source to drain-gate is seen as surface donor trap concentration is increased.

Fig. 5. Closer look at the current density contours for devices having dominating field peak near (a) field plate edge and (b) gate edge depicting drain—source leakage and gate—drain leakage for devices with lower and higher surface donor trap concentration, respectively.

with surface donor trap concentration (point  $B \to C$ ) as gate leakage dominates the drain current (Region II). This transition from Region I to Region II in Fig. 3(a) indicates a change in the breakdown phenomena governing device behavior as surface donor trap concentration is increased. Device behavior under conditions with suppressed gate leakage [metal-insulator-semiconductor (MIS) gated devices] will be discussed in later sections.

#### B. Modulation of Electric Field by Surface Traps

In order to further evaluate the breakdown phenomena and the shift in leakage paths/source governing breakdown, lateral electric field profile was extracted for devices with varying surface donor trap concentration. Fig. 3(b) depicts the lateral electric field at the onset of breakdown for different surface donor trap concentrations. The electric field is extracted in the channel region just below the drain–source contact edge [cut-line AA' in Fig. 2(a)]. The surface donor trap concentrations are selected to represent points A, B, and C in Fig. 3(a). The field profile shows presence of three peaks, which are near the gate contact edge  $(E_{P1})$ , field plate edge  $(E_{P2})$  and the drain contact edge  $(E_{P3})$ . For surface donor trap condition at A, electric field is confined near drain edge leading to higher magnitude of  $E_{P3}$ , resulting in a source—drain leakage current induced breakdown, as shown in Fig. 4(a).

On the other hand, for surface donor trap condition at B, electric field is redistributed between  $E_{P1}$ ,  $E_{P2}$ , and  $E_{P3}$  with  $E_{P2}$  being higher in magnitude. Under this condition, Figs. 4(b) and 5(a) show the channel region underneath the gate and field plate contact being depleted, while the leakage current flows through deeper GaN buffer with leakage path emanating from the field plate edge. This suggests carrier generation near-field plate edge to be responsible for the source—drain leakage current leading to device breakdown. This further establishes that device breakdown in this case

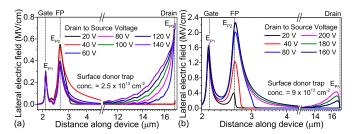

Fig. 6. Channel lateral electric field as a function of drain voltage for a surface donor trap concentration of (a)  $2.5 \times 10^{13}$  cm<sup>-2</sup> and (b)  $9 \times 10^{13}$  cm<sup>-2</sup>.

is determined by the magnitude of  $E_{P2}$ . Field redistribution between  $E_{P1}$ ,  $E_{P2}$ , and  $E_{P3}$  results in the observed improvement in  $V_{\rm BD}$  [Fig. 2(b)]. However, as the surface donor trap concentration is increased to point C,  $E_{P1}$  and  $E_{P2}$  increase considerably while  $E_{P3}$  reduces [Fig. 3(b)]. Furthermore, Figs. 4(c) and 5(b) depict leakage path from gate to drain electrode through the device channel, shifting the breakdown hot-spot to gate edge. Increase in surface donor trap concentration further leads to increase in magnitude of  $E_{P1}$ . This results in a fall in  $V_{BD}$  [Fig. 2(b)] when the breakdown hot-spot shifts near gate edge. The lateral electric field profile and leakage contours establish that with an increase in surface donor trap concentration, electric field peak determining device breakdown shifts from drain edge to gate edge. This results in an optimum field redistribution for certain range of surface donor trap concentration for which maximum  $V_{\rm BD}$  is observed.

It should be noted that Fig. 6(b) depicts that breakdown for the cases in which  $E_{P3}$  dominates is observed at much lower lateral field values. This is attributed to the breakdown being caused by higher vertical field near drain edge as the  $V_{\rm DS}$  appears across GaN buffer as well. A detailed account of impact of vertical field near the drain edge on  $V_{\rm BD}$  of the device is presented in our earlier work in [24]. As discussed in [24], vertical field depends on buffer properties and hence, can be neglected while analyzing impact of surface traps on  $V_{\rm BD}$ .

### C. Understanding the Dependence of Electric Field on Surface Trap Concentration

While the above discussion has established that a change in surface donor trap concentration modulates the lateral electric field, the physical mechanism governing this field modulation is not clear. To further probe into the impact of surface donor

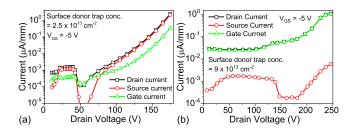

Fig. 7. Drain, gate, and source leakage current extracted in the OFF-state condition for AlGaN/GaN HEMT device with surface donor trap concentration of (a)  $2.5 \times 10^{13}$  cm<sup>-2</sup> and (b)  $9 \times 10^{13}$  cm<sup>-2</sup>. Breakdown at lower surface donor trap concentration is determined by increase in source leakage current for  $V_{\rm DS} > 60$  V, while gate leakage current determines breakdown for devices with higher surface donor trap concentration.

traps on channel electric field and  $V_{\rm BD}$ , the lateral electric field profile for different surface donor trap concentrations [point A and point C in Fig. 2(b)] was extracted as a function of applied drain–source voltage ( $V_{\rm DS}$ ). Fig. 6(a) and (b) depicts that at lower  $V_{\rm DS}$  (<40 V) electric field is confined in a narrow region near-field plate edge irrespective of the surface donor trap concentration. However, for device with lower surface donor trap concentration [Fig. 6(a)] electric field starts appearing at  $E_{P3}$  at much lower voltages ( $\sim$ 60 V in this case). Increasing  $V_{\rm DS}$  further adds to  $E_{P3}$  magnitude, which eventually leads to breakdown—characterized by increase in source—drain leakage current [Fig. 4(a)].

Furthermore, leakage characteristics, as shown in Fig. 7(a), reveal an increase in drain–source leakage current at  $\sim$ 60 V, which is similar to  $V_{\rm DS}$  at which magnitude of  $E_{P3}$  starts increasing [Fig. 6(a)]. This indicates a strong correlation between electric field peak near drain edge and drain–source leakage. On the other hand, Fig. 6(b) shows that a higher  $V_{\rm DS}$  is required for  $E_{P3}$  to increase considerably in case of higher surface donor trap concentration. It should be noted that, for a given  $V_{\rm DS}$ , magnitude of  $E_{P1}$  and  $E_{P2}$  is higher for devices with higher surface donor trap concentration. This is reflected in leakage characteristics shown in Fig. 7(b) where gate leakage dominates, and source leakage starts increasing at much higher values of  $V_{\rm DS}$  as compared to that for devices with lower surface donor trap concentration.

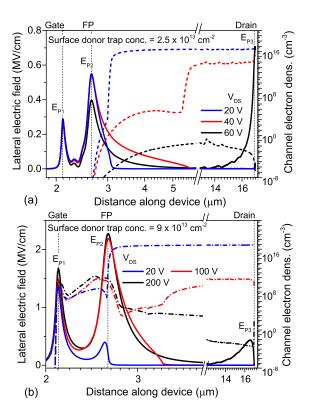

A comparison of channel depletion and lateral electric field profile in the channel region, shown in Fig. 8, establishes that channel depletion defines the channel electric field profile. Fig. 8(a) and (b) depict a significant impact of surface donor trap concentration on channel depletion. Fig. 8(a) shows that for devices with lower surface donor trap concentration, channel depletion up to drain edge takes place at a lower  $V_{\rm DS, \ depletion}$  ( $\sim$ 60 V) compared to devices with higher surface donor trap concentration ( $V_{\rm DS,\ depletion} \approx 200\ {\rm V}$ ). The discussion mentioned above establishes that extension of depletion region to the drain edge results in device breakdown due to increased source-drain leakage. On the other hand, confinement of depletion region near-field plate or gate edge results in a shift in breakdown hot-spot to gate edge. An optimum field redistribution results in maximum  $V_{\rm BD}$  for moderate surface donor trap concentrations.

Fig. 8. Channel electric field and electron density extracted for a surface donor trap concentration of (a)  $2.5 \times 10^{13}$  cm<sup>-2</sup> and (b)  $9 \times 10^{13}$  cm<sup>-2</sup>. The channel depletion modulation by surface donor trap concentration drives the change in lateral electric field affecting breakdown.

Above discussion establishes that an increase in surface donor trap density leads to requirement of a higher drain field to achieve similar depletion width ( $W_{\text{Depletion}}$ ). This effect can be attributed to three different mechanisms involved with surface donor traps, 1) modulation of channel charge density  $(n_S)$ ; 2) improved channel confinement; and 3) modulation of lateral electric field. An increase in surface donor trap concentration is known to result in an increase in  $n_S$  [27]. This will result in a reduction in  $W_{\text{Depletion}}$  for a given  $V_{\text{DS}}$ , as surface donor trap concentration is increased. However, Fermi level pinning at the surface leads to a saturation in  $n_S$  as surface donor trap concentration is increased to much higher values [27]. This should lead to a saturation in  $W_{\text{Depletion}}$  and  $V_{\rm BD}$  at higher surface donor trap concentrations. However, this does not completely explain the bell shaped curve obtained in Fig. 2(b). Further modulation of channel depletion and  $V_{\rm BD}$  can be explained by considering other two factors. Both the factors are attributed to positive charge being presented by ionized surface donor traps on the device surface. First, presence of a positive sheet charge on the device surface leads to a vertical electric field directed toward the substrate. This vertical electric field compliments the field due to polarization charges and improves channel confinement. Improved channel confinement now requires higher drain bias to deplete the channel and hence, a lower depletion width is observed for higher surface donor trap concentrations. Second, presence of a positive sheet charge on the device surface can have a lateral electric field component affecting the channel depletion

Fig. 9. Schematic of devices fabricated on similar GaN buffer but with different surface conditions with (a) having 40-nm  $\mathrm{Si}_3\mathrm{N}_4$  as surface passivation, while (b) has a surface passivation of 10-nm  $\mathrm{Al}_{0.52}\mathrm{Ti}_{0.48}\mathrm{O}$  grown on top of 30-nm  $\mathrm{Si}_3\mathrm{N}_4$ . (c) Comparison of EL intensity extracted along a line scan from gate field plate edge to drain edge for two devices fabricated according to schematic shown in (a) and (b), having different surface conditions.

as well. Computational findings discussed here suggest that this lateral component works opposite to the applied drain field leading to requirement of a higher  $V_{\rm DS}$  for achieving similar  $W_{\rm Depletion}$  (Fig. 8). This combined effect of lateral and vertical field components due to positive surface charge and  $n_S$  modulation leads to reduced depletion width as surface donor trap concentration is increased.

#### D. Experimental Validation

In order to validate the observed impact of surface donor trap concentration on channel electric field in the device, devices having similar processing and buffer conditions but with different surface conditions were fabricated using a well-established fabrication technique for AlGaN/GaN HEMTs [31]. A commercial grade 6" GaN-on-Si epi-stack was used to fabricate devices having in situ  $SiN_X$  passivation layer, as shown in Fig. 9(a). In order to have a surface variant, 10-nm  $SiN_X$  passivation was etched in one of the devices and a 10-nm Al<sub>0.52</sub>Ti<sub>0.48</sub>O was grown on the top of SiN<sub>X</sub> passivation [Fig. 9(b)]. Al<sub>0.52</sub>Ti<sub>0.48</sub>O is known to be p-type in nature and is expected to have negatively charged ions [31]. Under such conditions, having an Al<sub>0.52</sub>Ti<sub>0.48</sub>O on the top will reduce the effective positive surface charge density and hence, electric field profile in the two devices will be different. In order to estimate electric field profile, EL studies were done on the two devices having identical device parameters. EL line scans were done from gate field plate edge to drain edge for similar stress conditions. As EL intensity depends on the depletion width and number of carriers, EL line scan provides a good approximation of depletion width in the device channel. As per the observations presented above, devices with  $SiN_X/Al_{0.52}Ti_{0.48}O$  as passivation, having lower positive surface charge density, should show a wider depletion region as compared to devices with only  $SiN_X$  as passivation.

The EL line scan results, as shown in Fig. 9(c), depict that devices having  $SiN_X$  as passivation have an EL intensity peak near the field plate edge which rapidly reduces as we move away from the field plate depicting minimum field redistribution in the gate–drain access region. On the other hand, devices having  $SiN_X/Al_{0.52}Ti_{0.48}O$  as passivation show

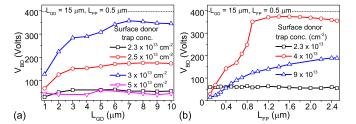

Fig. 10. Impact of device scaling on  $V_{\rm BD}$  of the device extracted as a function of surface donor trap concentration. (a) Scaling with respect to  $L_{\rm GD}$  for a constant  $L_{\rm FP}$  of 250 nm and (b) denotes scaling with respect to  $L_{\rm FP}$  for an  $L_{\rm GD}$  of 5  $\mu$ m. Shorter device dimensions are used here to highlight the relevance of developed physical insights in improving  $V_{\rm BD}$  of the device while using shorter  $L_{\rm GD}$  and  $L_{\rm FP}$ . Dashed line here represents the best  $V_{\rm BD}$  achieved with the larger device geometry, shown in Fig. 2(a).

a completely different profile with a considerable EL intensity redistribution in the access region with significantly higher EL intensity near the drain edge as well. This indicates a wider depletion region as compared to devices with  $SiN_X$  as passivation. These observations are in complete agreement with the computational findings discussed above.

# IV. DEVICE DESIGN IN PRESENCE OF SURFACE TRAPS A. Drift Region Engineering in Presence of Surface Traps

Fig. 10(a) depicts impact of increasing gate to drain length  $(L_{\rm GD})$  on  $V_{\rm BD}$  of the device as a function of surface donor trap concentration. It interestingly depicts negligible scaling with  $L_{\rm GD}$  for devices with lower surface donor trap concentration  $(\sim 2.3 \times 10^{13} \text{ cm}^{-2})$ . As the surface donor trap concentration is increased, devices show an improvement in  $V_{\rm BD}$  as  $L_{\rm GD}$ is increased. However, increasing the surface donor trap concentration to much higher values again results in negligible change in  $V_{\rm BD}$  as  $L_{\rm GD}$  is increased. A comparison of lateral channel electric field in devices with lower surface donor trap concentration, shown in Fig. 11(a), for different  $L_{GD}$  values reveals negligible field redistribution in the gate-drain access region. The electric field in these cases is confined near the drain contact edge [Fig. 11(a)]. On the other hand, devices with higher surface donor trap concentration exhibit a field redistribution in the gate-drain access region with increase in magnitude of  $E_{P1}$  and  $E_{P2}$  [Fig. 11(b)]. This results in an increase in  $V_{\rm BD}$  as  $L_{\rm GD}$  is increased. This field redistribution is in-line with the dependence of channel electric field on surface trap concentration discussed above. For moderate surface donor trap concentration, an optimum field redistribution in the gate-drain access region is observed [Fig. 11(b)] resulting in maximum  $V_{\rm BD}$  improvement when  $L_{\rm GD}$  was increased. Further increase in surface donor trap concentration results in a confinement of electric field near the gate edge with negligible redistribution in the gate-drain access region [Fig. 11(b)]. This leads to negligible change in  $V_{\rm BD}$  when  $L_{\rm GD}$  was increased.

$V_{\rm BD}$  as a function of gate-connected field plate length ( $L_{\rm FP}$ ) is shown in Fig. 10(b). It shows that the devices with lower surface donor trap concentration ( $\sim 2.3 \times 10^{13}~{\rm cm}^{-2}$ ) exhibit an  $L_{\rm FP}$  independent breakdown phenomena. On the other hand, devices having moderate surface donor trap concentration show excellent  $V_{\rm BD}$  scaling with increase in  $L_{\rm FP}$ . For higher

Fig. 11. Lateral electric field profile depicting impact of surface donor trap concentration on lateral field distribution as prominent field peak shifts from drain edge to gate edge. (a) Compares two devices having  $E_{P3}$  as prominent peak and (b) compares devices with  $E_{P1}$  and  $E_{P2}$  as prominent peak.

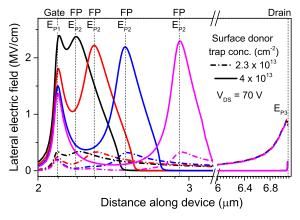

Fig. 12. Electric field profile for devices with different field plate lengths depicts field redistribution with field plate length in devices having prominent electric field peak near the gate edge.

surface donor trap concentration,  $V_{\rm BD}$  improvement with increase in  $L_{\rm FP}$  is seen but with a reduced  $V_{\rm BD}$  as compared to devices with moderate surface donor trap concentration. A comparison of electric field under two different surface donor trap concentrations, as shown in Fig. 12, explains the dependence of  $V_{\rm BD}-L_{\rm FP}$  scaling on surface donor trap concentration. For lower surface donor trap concentrations,  $E_{P3}$  is prominent which is independent of gate field plate

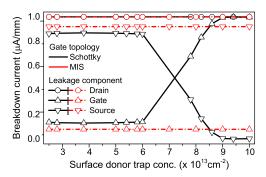

Fig. 13. (a)  $V_{\rm BD}$  as a function of surface donor trap concentration for Schottky and MIS gated devices depicting a similar dependence of  $V_{\rm BD}$  on trap concentration for both the cases. (b) Channel lateral electric field profile as a function of surface donor trap concentration for MIS gated devices, extracted at a drain stress voltage of 100 V.

design. Under such conditions, field plate is ineffective in field redistribution resulting in  $L_{\rm FP}$  independent  $V_{\rm BD}$ . On the other hand,  $E_{P1}$  starts becoming prominent as surface donor trap concentration is increased. Under such conditions, Fig. 12 depicts a relaxation in magnitude of  $E_{P1}$  as  $L_{FP}$  is increased, which results in an improvement in  $V_{\rm BD}$ . This relaxation is attributed to field redistribution between  $E_{P1}$  and  $E_{P2}$ . This establishes that a larger field plate is required for devices having trappy surface or trappy passivation interface. It is worth highlighting that the observed electric field redistribution wherein a shift in prominent electric field peak from  $E_{P3}$ to  $E_{P1}$  is seen as surface donor trap concentration is increased is attributed to channel depletion modulation by positively ionized surface donors, as discussed in Section III-C. Furthermore, as surface passivation layers modulate surface donor trap conditions and hence, affect channel electric field (Fig. 9), device design under such conditions needs to be considered carefully in light of these observations.

#### B. Impact of Gate-Stack

Fig. 3(a) showed a change in breakdown phenomena by highlighting that breakdown at higher surface donor trap concentrations is determined by gate leakage. However, subsequent electric field based analysis revealed that a shift in electric field peak from drain edge to gate edge determines the  $V_{\rm BD}$ . In order to analyze how suppressing gate leakage affects dependence of channel electric field on surface donor traps, devices with (MIS gate-stack having 10-nm thick  $Si_3N_4$ as gate dielectric were simulated. Since gate-stack process involves surface cleaning or surface treatment to minimize the defect concentration at the Gate-Oxide/AlGaN (MIS) interface, TCAD framework used in this work also considered a fixed trap concentration at the MIS interface. The same was calibrated to give a threshold voltage similar to that of Schottky devices, ensuring breakdown measurement under similar stress conditions. It should also be noted that the surface trap concentration, however, was varied only at the AlGaN surface/passivation interface in the gate-drain and gate-source access regions. Fig. 13(a) depicts a similar dependence of  $V_{\rm BD}$ on surface donor trap concentration for both Schottky gated as well as MIS gated devices.

Fig. 13(b), depicts a shift in electric field peak from drain contact edge to gate contact edge as surface donor trap

Fig. 14. Comparison of different leakage current components at the onset of breakdown extracted for Schottky and MIS gated devices depicting breakdown in MIS gated devices to be determined by source leakage even at higher surface donor trap concentrations.

Fig. 15. Electron current density contours at the onset of breakdown extracted for different surface donor trap concentrations. These contours depict a shift in breakdown hot-spot from drain edge to gate edge with increase in surface donor trap concentration for MIS gated devices as well.

concentration is increased for MIS gated devices. This behavior is similar to that observed for Schottky gated devices [Fig. 6(a) and (b)]. This establishes that the dependence of channel electric field on surface donor trap concentration is independent of gate-stack design or gate leakage. The only difference is that with suppressed gate leakage in presence of MIS structure beneath gate contact, as shown in Figs. 14 and 15, the breakdown for the complete range of surface donor trap concentration considered here is dominated by drain–source leakage.

The drain–source leakage path—originating from peak electric field location, as depicted in Fig. 15, changes as a function of surface donor trap concentration. For lower surface donor trap concentration [Fig. 15(a)], leakage path is from drain contact edge to source contact, indicating the breakdown hot-spot to be near drain edge. However, for higher surface donor trap concentration [Fig. 15(b)], the leakage path emanates from the field plate edge, indicating shift in breakdown hot-spot to field

plate edge. This establishes that with change in gate-stack and suppression of gate leakage current, while the dominant leakage current and leakage path changes, the electric field, and breakdown behavior remain similar to that observed for Schottky gate. Therefore, it can be fairly concluded that the phenomena and device design discussed in this work are applicable to MIS and other gate architectures as well.

#### V. CONCLUSION

Through detailed and calibrated computational analysis, we have found that donor traps present on device surface have a significant impact on breakdown characteristics of AlGaN/GaN HEMTs. Electric field modulation by surface donor traps was found to be the primary mechanism governing the breakdown characteristics of the device. A shift in breakdown hot-spot from drain edge to gate edge was seen with an increase in surface donor trap concentration. Experimental analysis of electric field modulation under different surface passivation conditions was found to be in complete agreement with the computational findings. Finally, impact of surface donor traps on designing of devices for high breakdown voltage was discussed with respect to field plate length, gate-drain distance and gate-stack. Dependence of breakdown voltage on surface donor trap concentration, till moderate concentrations, was found to remain unchanged even when gate leakage was suppressed by using a gate insulator. However, for very high surface donor trap concentrations, MIS gate offers higher breakdown voltage when compared to Schottky gate. It was found that the improvement in breakdown voltage while increasing gate-to-drain distance occurs only for moderate surface donor trap concentrations. On the other hand, breakdown voltage showed strong dependence on field plate length only for relatively higher surface donor trap concentrations. Therefore, the optimum field plate length and gate-drain distance to maximize breakdown voltage for a given buffer thickness strongly depends on the nature of surface passivation. A hybrid approach to passivate surface donor traps leaving higher surface donor trap concentration under field plate and moderate trap concentration in rest of the region can potentially maximize the breakdown voltage for a given gateto-drain spacing, field plate length and GaN buffer thickness.

#### **ACKNOWLEDGMENT**

Sayak Dutta Gupta and Rajarshi Roy Chaudhuri would like to thank DST INSPIRE for their fellowship.

#### REFERENCES

- [1] M. Grupen, "Reproducing GaN HEMT kink effect by simulating field-enhanced barrier defect ionization," *IEEE Trans. Electron Devices*, vol. 66, no. 9, pp. 3777–3783, Sep. 2019, doi: 10.1109/ted.2019.2928536.

- [2] V. Joshi, B. Shankar, S. P. Tiwari, and M. Shrivastava, "Dependence of avalanche breakdown on surface & buffer traps in AlGaN/GaN HEMTs," in *Proc. Int. Conf. Simul. Semiconductor Processes Devices (SISPAD)*, Sep. 2017, pp. 109–112, doi: 10.23919/sispad.2017.8085276.

- [3] Y. Saito, R. Tsurumaki, N. Noda, and K. Horio, "Analysis of reduction in lag phenomena and current collapse in field-plate AlGaN/GaN HEMTs with high acceptor density in a buffer layer," *IEEE Trans. Device Mater. Rel.*, vol. 18, no. 1, pp. 46–53, Mar. 2018, doi: 10.1109/tdmr.2017.2779429.

- [4] G. Verzellesi et al., "Influence of buffer carbon doping on pulse and AC behavior of insulated-gate field-plated power AlGaN/GaN HEMTs," IEEE Electron Device Lett., vol. 35, no. 4, pp. 443–445, Apr. 2014, doi: 10.1109/led.2014.2304680.

- [5] S. Yang, C. Zhou, S. Han, J. Wei, K. Sheng, and K. J. Chen, "Impact of substrate bias polarity on buffer-related current collapse in AlGaN/GaNon-Si power devices," *IEEE Trans. Electron Devices*, vol. 64, no. 12, pp. 5048–5056, Dec. 2017, doi: 10.1109/ted.2017.2764527.

- [6] M. Tao et al., "Buffer-induced time-dependent OFF-state leakage in AlGaN/GaN high electron mobility transistors on silicon," *IEEE Trans. Electron Devices*, vol. 63, no. 12, pp. 4860–4864, Dec. 2016, doi: 10.1109/ted.2016.2614332.

- [7] W. M. Waller, M. Gajda, S. Pandey, J. J. T. M. Donkers, D. Calton, J. Croon, J. Šonský, M. J. Uren, and M. Kuball, "Control of buffer-induced current collapse in AlGaN/GaN HEMTs using SiN<sub>x</sub> deposition," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4044–4049, Oct. 2017, doi: 10.1109/TED.2017.2738669.

- [8] J. T. Asubar et al., "Current collapse reduction in AlGaN/GaN HEMTs by high-pressure water vapor annealing," IEEE Trans. Electron Devices, vol. 62, no. 8, pp. 2423–2428, Aug. 2015, doi: 10.1109/ted.2015.2440442.

- [9] A. P. Edwards, J. A. Mittereder, S. C. Binari, D. S. Katzer, D. F. Storm, and J. A. Roussos, "Improved reliability of AlGaN–GaN HEMTs using an NH<sub>3</sub> plasma treatment prior to SiN passivation," *IEEE Electron Device Lett.*, vol. 26, no. 4, pp. 225–227, Apr. 2005, doi: 10.1109/led.2005.844694.

- [10] M. J. Uren et al., "'Leaky dielectric' model for the suppression of dynamic R<sub>ON</sub> in carbon-doped AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 64, no. 7, pp. 2826–2834, Jul. 2017, doi: 10.1109/TED.2017.2706090.

- [11] J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors," *Appl. Phys. Lett.*, vol. 77, no. 2, pp. 250–252, Jul. 2000, doi: 10.1063/1.126940.

- [12] A. D. Koehler et al., "Impact of surface passivation on the dynamic ON-resistance of proton-irradiated AlGaN/GaN HEMTs," IEEE Electron Device Lett., vol. 37, no. 5, pp. 545–548, May 2016, doi: 10.1109/led.2016.2537050.

- [13] S.-C. Liu, B.-Y. Chen, Y.-C. Lin, T.-E. Hsieh, H.-C. Wang, and E. Y. Chang, "GaN MIS-HEMTs with nitrogen passivation for power device applications," *IEEE Electron Device Lett.*, vol. 35, no. 10, pp. 1001–1003, Oct. 2014, doi: 10.1109/led.2014.2345130.

- [14] H.-S. Kim et al., "Normally-off GaN-on-Si MISFET using PECVD SiON gate dielectric," IEEE Electron Device Lett., vol. 38, no. 8, pp. 1090–1093, Aug. 2017, doi: 10.1109/led.2017.2720719.

- [15] R. Hao et al., "Breakdown enhancement and current collapse suppression by high-resistivity GaN cap layer in normally-off AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 38, no. 11, pp. 1567–1570, Nov. 2017, doi: 10.1109/led.2017.2749678.

- [16] S. Gao, Q. Zhou, X. Liu, and H. Wang, "Breakdown enhancement and current collapse suppression in AlGaN/GaN HEMT by NiO<sub>X</sub>/SiN<sub>X</sub> and Al<sub>2</sub>O<sub>3</sub>/SiN<sub>X</sub> as gate dielectric layer and passivation layer," *IEEE Electron Device Lett.*, vol. 40, no. 12, pp. 1921–1924, 2019, doi: 10.1109/LED.2019.2945175.

- [17] A. Koudymov, V. Adivarahan, J. Yang, G. Simin, and M. A. Khan, "Mechanism of current collapse removal in field-plated nitride HFETs," *IEEE Electron Device Lett.*, vol. 26, no. 10, pp. 704–706, Oct. 2005, doi: 10.1109/led.2005.855409.

- [18] W. Saito, M. Kuraguchi, Y. Takada, K. Tsuda, I. Omura, and T. Ogura, "Influence of surface defect charge at AlGaN–GaN-HEMT upon Schottky gate leakage current and breakdown voltage," *IEEE Trans. Electron Devices*, vol. 52, no. 2, pp. 159–164, Feb. 2005, doi: 10.1109/ted.2004.842710.

- [19] H. Hanawa, H. Onodera, A. Nakajima, and K. Horio, "Numerical analysis of breakdown voltage enhancement in AlGaN/GaN HEMTs with a high-k passivation layer," *IEEE Trans. Electron Devices*, vol. 61, no. 3, pp. 769–775, Mar. 2014, doi: 10.1109/ted.2014.2298194.

- [20] M. Borga et al., "Modeling of the vertical leakage current in AlN/Si heterojunctions for GaN power applications," *IEEE Trans. Electron Devices*, vol. 67, no. 2, pp. 595–599, Feb. 2020, doi: 10.1109/ted.2020.2964060.

- [21] J. Sun et al., "Substantiation of buried two dimensional hole gas (2DHG) existence in GaN-on-Si epitaxial heterostructure," Appl. Phys. Lett., vol. 110, no. 16, Apr. 2017, Art. no. 163506, doi: 10.1063/1.4980140.

- [22] L. Sayadi et al., "The role of silicon substrate on the leakage current through GaN-on-Si epitaxial layers," *IEEE Trans. Electron Devices*, vol. 65, no. 1, pp. 51–58, Jan. 2018, doi: 10.1109/ted.2017.2773670.

- [23] J. Hu et al., "Time-dependent breakdown mechanisms and reliability improvement in edge terminated AlGaN/GaN Schottky diodes under HTRB tests," *IEEE Electron Device Lett.*, vol. 38, no. 3, pp. 371–374, Mar. 2017, doi: 10.1109/led.2017.2661482.

- [24] V. Joshi, S. P. Tiwari, and M. Shrivastava, "Part I: Physical insight into carbon-doping-induced delayed avalanche action in GaN buffer in AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 561–569, Jan. 2019, doi: 10.1109/ted.2018.2878770.

- [25] Z. Tang, S. Huang, Q. Jiang, S. Liu, C. Liu, and K. J. Chen, "High-voltage (600-V) low-leakage low-current-collapse AlGaN/GaN HEMTs with AlN/SiN<sub>x</sub> passivation," *IEEE Electron Device Lett.*, vol. 34, no. 3, pp. 366–368, Mar. 2013, doi: 10.1109/LED.2012.2236638.

- [26] V. Joshi, S. P. Tiwari, and M. Shrivastava, "Part II: Proposals to independently engineer donor and acceptor trap concentrations in GaN buffer for ultrahigh breakdown AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 570–577, Jan. 2019, doi: 10.1109/ted.2018.2878787.

- [27] V. Joshi, A. Soni, S. P. Tiwari, and M. Shrivastava, "A comprehensive computational modeling approach for AlGaN/GaN HEMTs," *IEEE Trans. Nanotechnol.*, vol. 15, no. 6, pp. 947–955, Nov. 2016, doi: 10.1109/tnano.2016.2615645.

- [28] D. Bisi et al., "Deep-level characterization in GaN HEMTs—Part I: Advantages and limitations of drain current transient measurements," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3166–3175, Oct. 2013, doi: 10.1109/ted.2013.2279021.

- [29] D. Cornigli et al., "Numerical investigation of the lateral and vertical leakage currents and breakdown regimes in GaN-on-silicon vertical structures," in *IEDM Tech. Dig.*, Dec. 2015, pp. 3–5, doi: 10.1109/iedm.2015.7409633.

- [30] F. Monti et al., "Numerical study of GaN-on-Si HEMT breakdown instability accounting for substrate and packaging interactions," in Proc. IEEE 27th Int. Symp. Power Semiconductor Devices IC's (ISPSD), May 2015, pp. 381–384, doi: 10.1109/ispsd.2015.7123469.

- [31] S. Dutta Gupta et al., "Positive threshold voltage shift in AlGaN/GaN HEMTs and E-mode operation by Al<sub>x</sub>Ti<sub>1-x</sub>O based gate stack engineering," *IEEE Trans. Electron Devices*, vol. 66, no. 6, pp. 2544–2550, Jun. 2019, doi: 10.1109/TED.2019.2908960.